從電路的角度看功耗

本文將從分兩部分進行講解,第一部分為CMOS電晶體的基礎知識,第二部分詳細闡述了電路中功耗組成。

CMOS Transistors

最早期的電子電腦使用繼電器或電子管實現二值系統,而現代電腦中則採用電晶體來實現二值系統。電晶體可以根據控制端電壓或者電流的變化來實現「開啟」或者「關閉」的功能,從而表達二進位。電晶體主要分為雙極性電晶體(Bipolar Junction Transistor)和金屬-氧化物半導體場效應電晶體(Metal Oxide Semiconductor Field Effect Transistor, MOSFET or MOS),當前絕大多數CPU都採用MOS電晶體實現,其中又以CMOS(Complementary Metal Oxide Semiconductor)電晶體電路設計最為常見。

Semiconductor

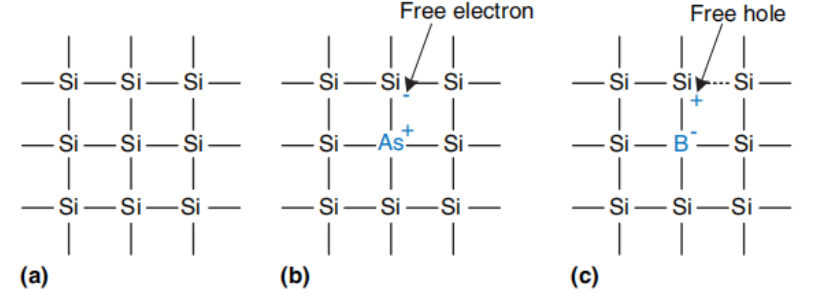

MOS電晶體使用硅作為基本材料,在元素周期表中,硅是IV族元素,他的原子最外層有4個電子,可以與相鄰的4個硅原子的最外層電子配對成為共價鍵,通過與相鄰原子形成的共價鍵,純凈硅中所有原子的最外層都具有8個電子,達到相對穩定,所以純凈硅的導電性很弱。

但是如果在純凈硅中摻雜少量的5價原子(如磷As),這些原子將擠占原有硅原子的位置,由於這些原子的最外層有5個電子,除了與原有的硅原子形成共價鍵用掉四個電子外,還多餘一個處於遊離狀態的電子。在電場的作用下,處於遊離狀態的電子會逆著電場的方向流動,形成負電流,這類材料被稱為n-type材料。

同樣如果在純凈的硅中摻雜少量的3價原子(如硼B),這些原子擠占原有硅原子的位置後,其最外層還缺少一個電子和相鄰的硅原子形成共價鍵,形成空穴(hole),在電場的作用下,周圍的電子就會跑來填補這個空穴,從而留下一個新的空穴,相當於空穴也在順著電場的方向流動,形成正電流,這類材料被稱為P-type材料。

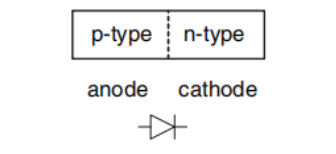

Diodes

p-type類型的硅和n-type類型的硅連接起來形成二極體(Diodes),p-type區域稱為陽極,n-type區域稱為陰極,當陽極電壓大於陰極電壓,電流從陽極流向陰極,反之陽極電壓小於陰極電壓,電流無法通過。

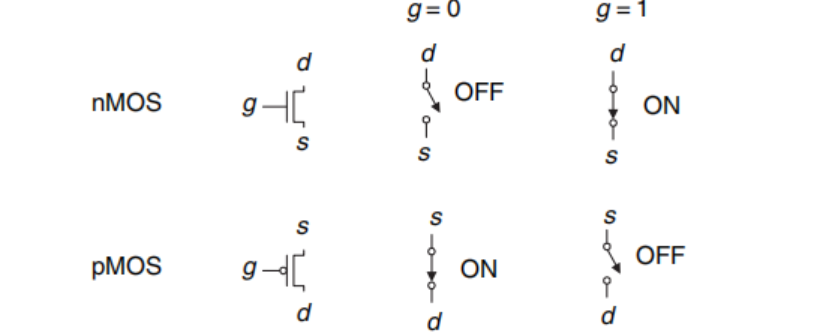

nMOS and pMOS Transistors

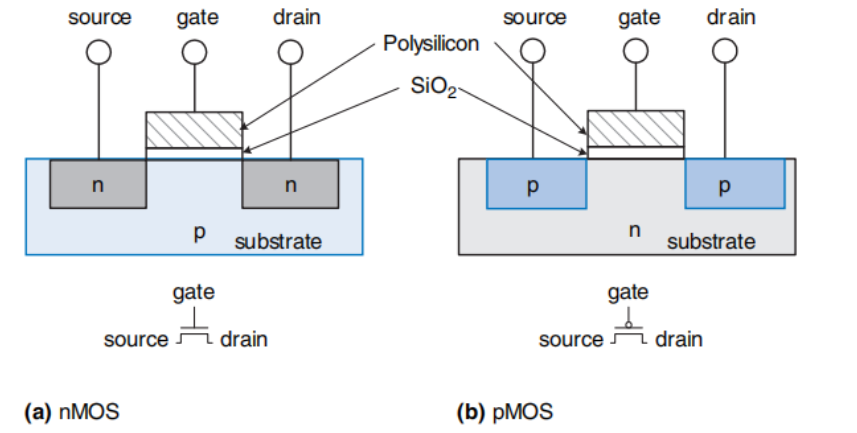

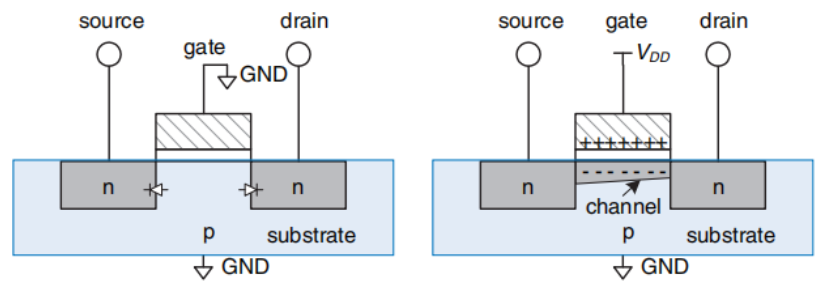

MOS電晶體是由多層摞放在一起的導電和絕緣材料構建起來的,每個電晶體的底部叫做襯底,是低濃度摻雜的半導體硅。電晶體上部接出來3個訊號埠,分別稱為源極(Source)、漏極(Drain)和柵極(Gate)。柵極和漏極叫做有源區,該區域採用與襯底相反極性的高濃度摻雜。襯底是低濃度P型摻雜,有源區是高濃度N型摻雜的MOS電晶體叫做nMOS電晶體;襯底是低濃度N型摻雜,有源區是高濃度P型摻雜的MOS電晶體叫做pMOS電晶體。

無論是nMOS管還是pMOS管,其柵極和襯底之間都存在一層絕緣體,叫做柵氧層,其成分通常是二氧化硅(silicon dioxide,SiO2)。最早期的MOS電晶體柵極由金屬製成,這也是metal-oxide-semiconductor名字的由來,現在大多數的柵極採用摻雜後的多晶硅(Polysilicon)製成。摻雜後的多晶硅儘管其電阻比金屬大,但卻比半導體硅的電阻小很多,可以用作電極。並且同普通金屬相比,多晶硅更耐受高溫,不至於在MOS電晶體生產過程中融化。

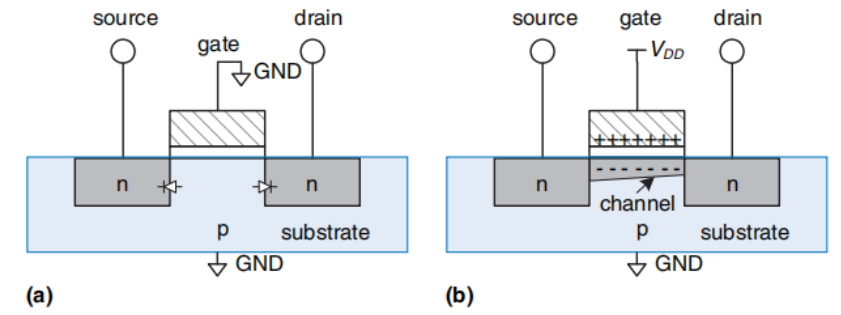

我們以nMOS電晶體為例,介紹電晶體如何工作

通常nMOS電晶體的襯底接地,如果單純在源極、漏極之間加上電壓,兩極之間是不會有電流流過的,因為源極和漏極之間相當於有一對正反相對的PN接面,如果在柵極上加上電壓,因為柵氧層是絕緣的,就會在P襯底里形成一個電場。柵極上的正電壓會把P襯底裡面的電子吸引到柵氧層的地步,形成一個很薄的溝道電子層,相當於在源極和漏極之間架起了一座導電的橋樑,此時再在源極漏極之間加上電壓,那麼兩極之間的電流就能流過來了。

pMOS正好相反,其襯底連接正電壓,當柵極不加電時,電晶體導通,柵極加電時,電晶體斷開。

隨著製程的發展,MOS電晶體中的柵氧層的厚度越來越薄,使得開啟所需要的門電壓不斷降低,從早期製程的5V,降低到後來的2.5V、1.8V,現在都是1V左右或者更低。

不幸的是,MOS電晶體不是理想的開關,nMOS電晶體適合傳輸0而不適合傳輸1,pMOS電晶體適合傳輸1而不適合傳輸0。因此需要同時使用兩種類型的電晶體,令他們傳輸自己的擅長的,這種處理過程稱為Complementary MOS or CMOS。

Common CMOS Gate

下面舉兩個簡單的例子來說明如何用cMOS電晶體來構造電路中的基本單元—門。

-

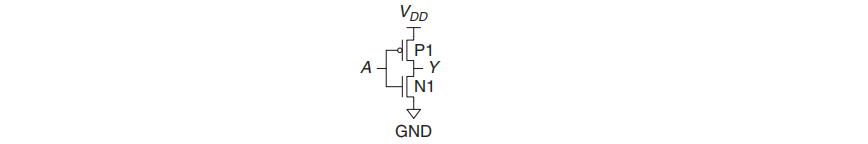

CMOS NOT Gate

當A為1,上面的pMOS電晶體斷開,下面的nMOS電晶體導通,Y = 0

當A為0,上面的pMOS電晶體導通,下面的pMOS電晶體斷開,Y = 1

-

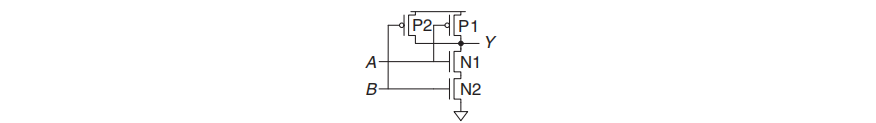

CMOS NAND Gate

通過並聯的pMOS電晶體和串聯的nMOS電晶體形成與非門,需要注意的是,當輸入即扇入係數過多時,串聯的nMOS會導致過大的延遲,因此通常扇入係數最多為4或5。

Power and Energy Consumption

功耗通常分為兩部分:

$$

P = P_{static} + P_{dynamic}

$$

-

Dynamic Power

電訊號在0和1之間變換時電容的充放電。

$$

P_{dynamic} = α * C_L * V^2_{DD} * f + I_{sc} * V_{DD}

$$

$C_L$為電路中的電容大小,$f$為時鐘頻率,$α$為電晶體翻轉的概率,$I_{SC}$ 為短路電流,$V_{DD}$ 為供電電壓(Supply voltage)。短路電流發生的原因為電訊號在0和1之間變化時,NMOS和PMOS電晶體同時導通,此時從$V_{DD}$到$GND$之間出現短路,通常短路電流功耗占功耗的一小部分,我們不做考慮。 -

Static Power

電訊號不發生變化時的功耗(電流泄露)

$$

P_{static} = V_{DD} * I_{D}

$$

$I_{D}$被稱為泄露電流(從$V_{DD}$到GND)

Static Power

重新回顧一下電晶體導通時的情況,當Gate端電壓達到一定值時,substrate上形成一個channel,此時電子可以流通,此時電晶體處於導通狀態。我們將source和drain導通所需要的電壓,我們記為$V_{TH}$,Gate端電壓記為$V_{GS}$。

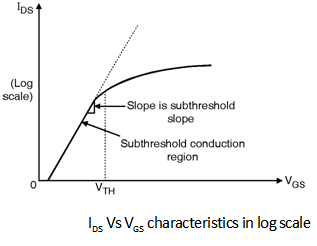

當$V_{GS} < V_{TH}$時,理想狀態下,source端和drain端無電流流動,但實際上,兩端之間仍存在電流流通,我們稱該電流為subthreshold current,記為$I_{D}$,泄露電流隨著gate端電壓增長指數級增長。

$$

I_{\text{D}}\approx I_{\text{D0}}e^{\frac {V_{\text{GS}}-V_{\text{TH}}}{nV_{\text{T}}}}

$$

$I_{D0}$為當$V_{GS} = V_{TH}$時的電流,$V_{T} = kT/q$為熱電壓(thermal voltage),我們需要關心的是泄露電流隨著門限電壓的降低指數級增長,因此門限電壓不能無限制的降低,這也限制了供電電壓的降低。

上圖刻畫了$I_{D}$和$V_{GS}$的關係(兩邊同時取log),通常一個好的電路,其Slope越大越好。

補充一個概念:thermal runaway,由於泄露電流會導致溫度提升,造成熱電壓的升高,此時泄露電流繼續增大,形成惡性循環,這種循環成為thermal runaway。因此經常說溫度是積體電路的第一殺手[^3]。

Dynamic Power

不考慮短路功耗,則動態功耗由下式表示:

$$

P_{dynamic} = α * C_L * V^2_{DD} * f

$$

動態功耗通常在功耗中佔比很高,是我們研究的重中之重。我們先來簡要說一下頻率和供電電壓的關係,這對我們後續理解大有幫助。

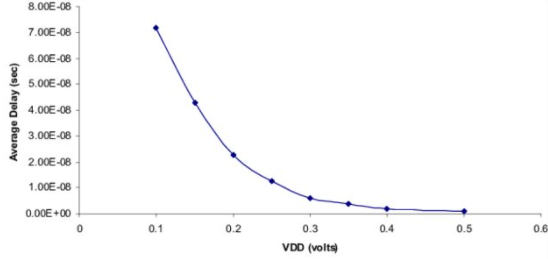

頻率$f$可以視為電路中關鍵路徑延遲的倒數,即$f = 1 / Delay $

而延遲通常由路徑中電容的充放電決定,延遲和供電電壓關係可以由下式給出[^5]

$$

Delay = C_L * V_{DD} / I = (C_L * V_{DD}) / (uC_{ox}(W / L)(V_{DD} – V_{TH})^2)

$$

可以看出延遲和供電電壓成反比

最終,我們將式子簡化為

$$

f \propto (V_{DD} – V_{TH})^2 / V_{DD}

$$

因此頻率可以看作電壓的線性函數,最大頻率隨著供電電壓的增加線性增加,所以動態功耗近似正比於供電電壓的三次方($P_{dynamic} \propto V^3$),因此在動態功耗為主的CPU中,通過動態降低電壓實現功耗降低帶來了很大的受益,但需要注意的是,降低$V_{DD}$也通常也意味著$f$的降低,會造成任務執行時間的增加,因此需要在performance和energy之間做出權衡,通常對於已知deadline time的任務,通過降低供電電壓且保證任務在期限前完成可以造成功耗大幅度下降。

Reference

[1] 《Digital Design and Computer Architecture》

[2] 《Embedded Computing for High Performance》

[3] 《電腦體系結構基礎(第二版)》 胡偉武著

[4] T. D. Burd and R. W. Brodersen, “Energy efficient CMOS microprocessor design,” Proceedings of the Twenty-Eighth Annual Hawaii International Conference on System Sciences, 1995, pp. 288-297 vol.1, doi: 10.1109/HICSS.1995.375385.

[5] A. P. Chandrakasan, S. Sheng and R. W. Brodersen, “Low-power CMOS digital design,” in IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, April 1992, doi: 10.1109/4.126534.

[6] T. Mudge, “Power: a first-class architectural design constraint,” in Computer, vol. 34, no. 4, pp. 52-58, April 2001, doi: 10.1109/2.917539.