FPGA內部IP核DDS

項目當中需要正弦訊號與餘弦訊號,首先想到了DDS晶片,例如AD9833、AD9834。由於還需要用FPGA 做一些數據處理,後來乾脆直接用FPGA 內部的DDSIP核,同時根據IP核內部的相位累加埠,設置觸發訊號,使得觸發訊號更加準時,並且通過PSD 演算法計算有效值,相位差更小,精度更高。

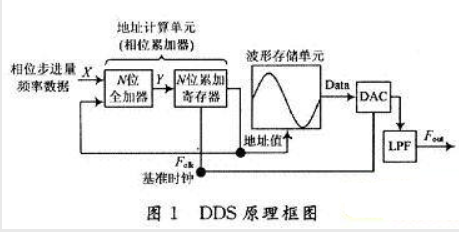

首先了解DDS的原理:

1、 DDS技術是根據奈奎斯特取樣定律,從連續訊號的相位出發,將正弦訊號取樣,編碼,量化,形成一個正弦函數表,存在EPROM中,合成時,通過改變相位累加器的頻率字來改變相位增量,也就是我們所稱的步長。相位增量的不同導致一個周期內取樣點的不同,在時鐘頻率即取樣頻率不變的情況下,通過相位的改變來改變頻率。

2、 DDS 以數控振蕩器的方式,產生頻率、相位可控制的正弦,電路包括了基準時鐘源、相位累加器、相位調製器、正弦ROM 查找表、D/A 轉換 器和低通濾波器等。 頻率控制字N 和相位控制字M 分別控制DDS 所輸出的正弦波的頻率和相 位。DDS 系統的核心是相位累加器,它由一個N 位累加器與N 位相位暫存器構成。時鐘脈衝每觸發一次, 累加器便將頻率控制數據與相位暫存器輸出的累加相位數據相加, 然後把相加後的結果送至相位暫存器的數據輸入端。 相位暫存器將累加器在上一個時鐘作用後所產生的新相位數據回饋到累加器的輸入端, 以使加法器在下一個時鐘的作用下繼續與頻率控制數據相加。 這樣, 相位累加器在參考時鐘的作用下將進行線性相位累加, 當相位累加器累加滿時, 就會產生一次溢出, 以完成一個周期性的動作, 這個周期就是DDS 合成訊號的一個頻率周期, 相位累加器的溢出頻率就是DDS 輸出的訊號頻率。 相位暫存器的輸出與相位控制字相加, 結果作為正弦查找表的地址。 查找表由ROM 構成, 其內部存有一個完整周期正弦波的數字幅度資訊, 每個查找表的地址對應正弦波中的一個相位點。 查找表把輸入地址資訊映射成正弦波幅度訊號, 同時輸出到D/A 轉換器的輸入端, 通過D/A 可將數字量形式的波形幅值轉換成所要求的合成頻率模擬量形式訊號。 低通濾波器用於衰減和濾除不需要的取樣分量, 以便輸出頻譜純凈的正弦波訊號。

ISE DDS IP核設置如下圖,輸出正弦訊號為12位,為了實現頻率的高解析度,需要將相位增加足夠的小,因此相位寬度為33位。

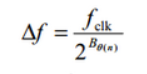

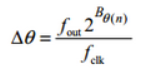

有DDS IP核datasheet當中,可以 看到解析度計算公式、相位增量公式如下:

當輸出38Khz正弦訊號,頻率分辨為0.01Hz,得到相位增量位寬為33位(50M/0.01=5000000000~~~~~~~BIT=33)

相位增量為38k*8589934592/50M=6528350。

wire [31:0] phase_out;

wire [32:0] poff_in;

assign poff_in = 33’d0;

wire [32:0] data_in; //DDS相位增量

assign data_in = 33’d6528350;

dds dds_inst_M0 (

.clk(clk), // input clk

.pinc_in(data_in), // input [32 : 0] pinc_in

.poff_in(poff_in), // input [32 : 0] poff_in

.cosine(cosine), // output [11 : 0] cosine

.sine(sine), // output [11 : 0] sine

.phase_out(phase_out) // output [32 : 0] phase_out

);

使用ModelSim模擬如下圖