FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833、AD9834。由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加端口,设置触发信号,使得触发信号更加准时,并且通过PSD 算法计算有效值,相位差更小,精度更高。

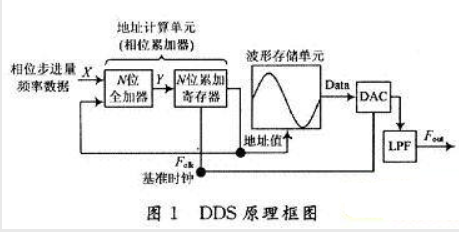

首先了解DDS的原理:

1、 DDS技术是根据奈奎斯特取样定律,从连续信号的相位出发,将正弦信号取样,编码,量化,形成一个正弦函数表,存在EPROM中,合成时,通过改变相位累加器的频率字来改变相位增量,也就是我们所称的步长。相位增量的不同导致一个周期内取样点的不同,在时钟频率即采样频率不变的情况下,通过相位的改变来改变频率。

2、 DDS 以数控振荡器的方式,产生频率、相位可控制的正弦,电路包括了基准时钟源、相位累加器、相位调制器、正弦ROM 查找表、D/A 转换 器和低通滤波器等。 频率控制字N 和相位控制字M 分别控制DDS 所输出的正弦波的频率和相 位。DDS 系统的核心是相位累加器,它由一个N 位累加器与N 位相位寄存器构成。时钟脉冲每触发一次, 累加器便将频率控制数据与相位寄存器输出的累加相位数据相加, 然后把相加后的结果送至相位寄存器的数据输入端。 相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端, 以使加法器在下一个时钟的作用下继续与频率控制数据相加。 这样, 相位累加器在参考时钟的作用下将进行线性相位累加, 当相位累加器累加满时, 就会产生一次溢出, 以完成一个周期性的动作, 这个周期就是DDS 合成信号的一个频率周期, 相位累加器的溢出频率就是DDS 输出的信号频率。 相位寄存器的输出与相位控制字相加, 结果作为正弦查找表的地址。 查找表由ROM 构成, 其内部存有一个完整周期正弦波的数字幅度信息, 每个查找表的地址对应正弦波中的一个相位点。 查找表把输入地址信息映射成正弦波幅度信号, 同时输出到D/A 转换器的输入端, 通过D/A 可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号。 低通滤波器用于衰减和滤除不需要的取样分量, 以便输出频谱纯净的正弦波信号。

ISE DDS IP核设置如下图,输出正弦信号为12位,为了实现频率的高分辨率,需要将相位增加足够的小,因此相位宽度为33位。

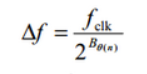

有DDS IP核datasheet当中,可以 看到分辨率计算公式、相位增量公式如下:

当输出38Khz正弦信号,频率分辨为0.01Hz,得到相位增量位宽为33位(50M/0.01=5000000000~~~~~~~BIT=33)

相位增量为38k*8589934592/50M=6528350。

wire [31:0] phase_out;

wire [32:0] poff_in;

assign poff_in = 33’d0;

wire [32:0] data_in; //DDS相位增量

assign data_in = 33’d6528350;

dds dds_inst_M0 (

.clk(clk), // input clk

.pinc_in(data_in), // input [32 : 0] pinc_in

.poff_in(poff_in), // input [32 : 0] poff_in

.cosine(cosine), // output [11 : 0] cosine

.sine(sine), // output [11 : 0] sine

.phase_out(phase_out) // output [32 : 0] phase_out

);

使用ModelSim仿真如下图