關於非同步複位同步釋放原理的詳細解答

- 2019 年 10 月 3 日

- 筆記

首先,本人查找了非同步複位同步釋放原理網路相關資料。大都沒有講清楚相關原理性的東西,令人困惱。

現花時間進行原理性的解答:理解為什麼非同步複位、同步釋放能夠實現?

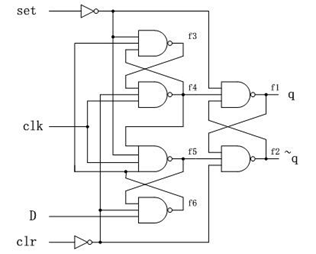

首先要知道複位D觸發器的工作原理,複位訊號作用於最後埠也作用於觸發器邏輯中間。

當複位端有效時(一般為1),複位訊號直接作用於最後一級的SR鎖存器(需要知道鎖存器的原理以及觸發器的原理,這個是電子的基礎),此時觸發器直接輸出q為0。

當複位訊號無效時(為0時),複位訊號為0,不能驅動最後一級SR鎖存器,此時輸出q=輸入的d,其中由時鐘訊號與複位訊號共同進行控制數據的變化,使q=d。

該圖為set,clr都為複位端的圖,我們理解時,使用單獨set進行理解。

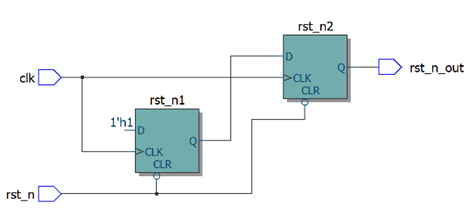

非同步複位、同步釋放。

module code ( clk,rst_n,rst_n_out); input clk; input rst_n; output rst_n_out; //wire rst_n_out_n; //輸入輸出沒定義類型,默認是wire型 reg rst_n1; reg rst_n2; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin rst_n1 <= 1'b0; rst_n2 <= 1'b0; end else begin rst_n1 <= 1'b1; rst_n2 <= rst_n1; end end assign rst_n_out = rst_n2; endmodule

先以rst_n為0,複位端即為1(將此時為複位狀態作起點),此時q1與q2同時由複位訊號rst_n控制,直接輸出為0。

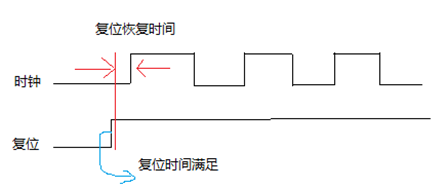

當rst_n從0變為1過程中時,此時複位端變為0,將無法直接作用與觸發器的輸出端。此時的狀態,q1由d1決定,q2由d2確定。此時由於q1有時鐘上升沿與複位訊號共同作用與第一觸發器

,由於d1為1,q1輸出將根據clk來決定,而此時由於時鐘與複位訊號已經作用與第二觸發器,此時d2為之前q1=0的狀態,由於d2為0,根據D觸發器的原理,無論clk為什麼,q2=0,於是q2繼續輸出為0。

當第一觸發器不滿足複位訊號與時鐘訊號的恢復時間時,即不滿足第一級觸發器內部延時,這個時候,第一級觸發器將發生亞穩態狀態,而此時第二級觸發器已經上升沿完畢,

需要等下一個上升沿才能繼續改變q2數據。

當亞穩態時間過去之後(亞穩態時間不會超過一個周期,超過一個周期仍然會影響到第二級觸發器),下一個周期時鐘來臨時,此時第一觸發器已經能夠正常的輸出為1,而第二觸發器也能夠直接等於d2,這時輸出rst_n_out = 1,完成複位。

也就是說非同步複位、同步釋放的本質就是,將原本由非同步複位訊號在有效時能直接作用於輸出端,改為延後一個周期通過在複位訊號無效時進行時鐘控制,即同步釋放。