數字邏輯實踐3->EDA技術與Verilog設計

本文屬於EDA技術概述類文章。對EDA技術現狀進行介紹。

1 EDA技術及其發展

概念

EDA(Electronic Design Automation),指的是以計算機為工作平台,以EDA軟件工具為開發環境,以PLD期間或者ASIC專用集成電路為目標期間設計實現電路系統的一種技術。

-

電子CAD(Computer Aided Design)

狹義的CAD 偏重於「製圖」和「建模」(幾何模型),廣義CAD即覆蓋了所有利用計算機進行輔助設計的過程,在這個意義上,CAE和EDA 也可以理解為是CAD的一種;

-

電子CAE(Computer Aided Engineering)

CAE的核心在於建模–解方程。

CAE 的關注點和出發點在於解決實際工程問題,無論是電磁仿真分析還是流體受力分析等實際問題在工程中都最終被抽象為了一個個數學方程,而得出仿真結果的過程就是求解數學問題的過程。

在CAE領域應用比較多的有有限元分析、有限差分法、加權餘量法等求解方程的經典方法,所以CAE的核心在於解方程,這一過程也凝聚了工程師的智慧輸出,所以說CAE和工程結合最為緊密,同時門檻極高;

-

EDA(Electronic Design Automation)

在CAD繪圖技術基礎上融合了應用電子技術、計算機技術、信息處理技術等實現電子產品的自動設計。

部分參考:

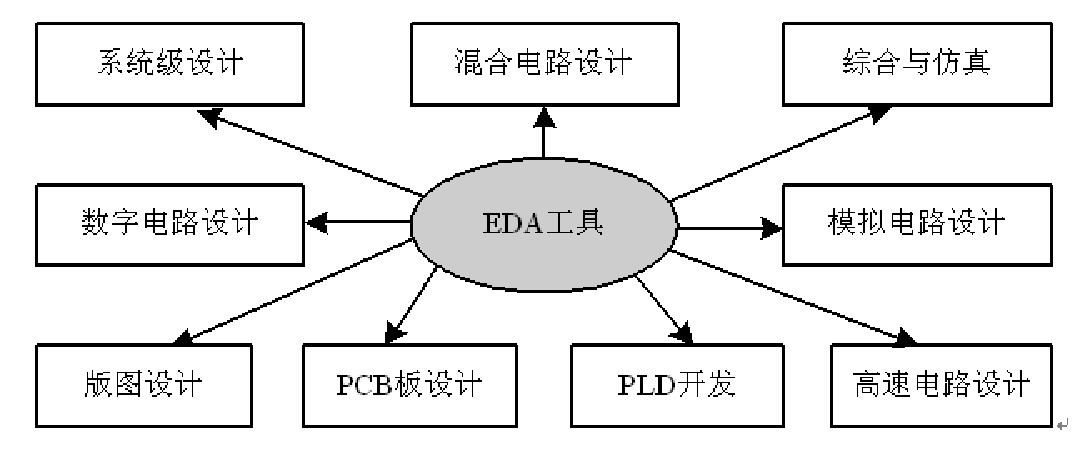

EDA技術的應用範疇

EDA技術的新發展

-

在FPGA上實現DSP應用

-

嵌入式處理器軟核的成熟

-

自主知識產權

-

電子技術領域全方位融入EDA技術

-

電子領域各學科的界限更加模糊、互為包容

-

更大規模的FPGA和CPLD器件不斷推出

-

IP核的廣泛應用

-

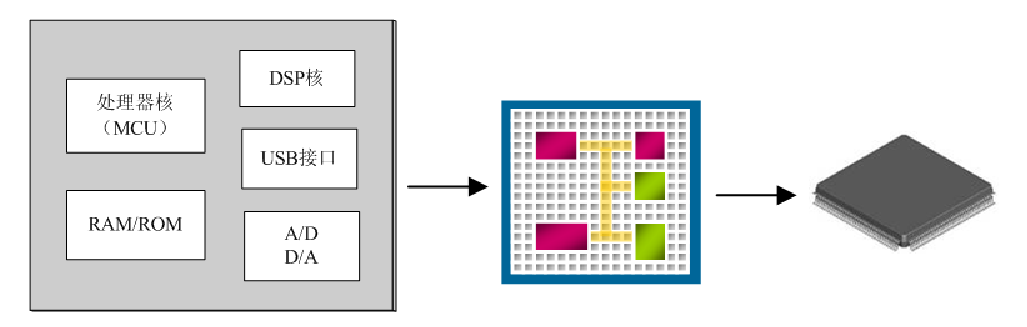

SoC高效低成本設計技術的成熟

現代EDA技術的特徵

-

硬件描述語言設計輸入

-

自頂向下設計方法(即 Top-down設計)

-

開放性和標準化

-

高層綜合與優化

2 Top-down設計與IP核設計

Top-down設計

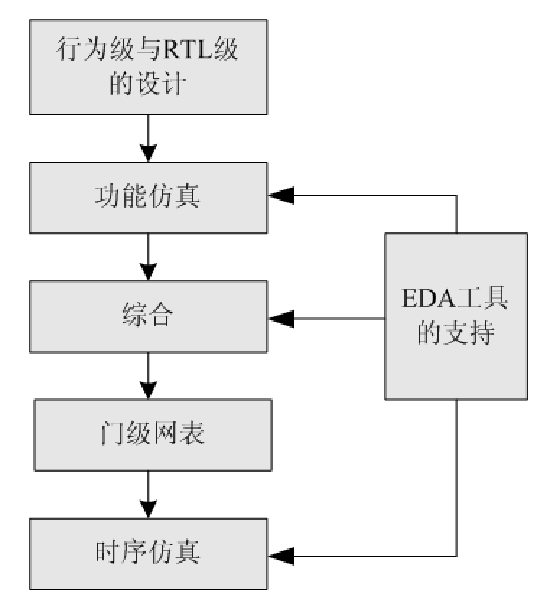

Top-down的設計須經過「設計—驗證—修改設計—再驗證」的過程,不斷反覆。

直到結果能夠實現所要求的功能,並在速度、功耗、價格和可靠性方面實現較為合理的平衡。

上圖就是自頂向下設計;

與之相對的是自底向上的設計(Bottom-up設計)👇

由設計者調用設計庫中的元件(如各種門電路、加法器、計數器等) ,設計組合出滿足自己需要的系統 缺點:效率低、易出錯

好傢夥,這不是Altuim Designer的設計風格嗎?

IP核設計

一些詞

-

IP(Intellectual Property):

原來的含義是指知識產權、著作權,在IC設計領域指實現某種功能的設計。

-

IP核(IP模塊):

指功能完整,性能指標可靠,已驗證的、可重用的電路功能模塊。

-

IP復用(IP reuse)

-

簡稱調包

IP核與SOC設計

軟IP–用VHDL等硬件描述語言描述的功能塊,但是並不涉及用什麼具體電路元件實現這些功能。

固IP–完成了綜合的功能塊。

硬IP–供設計的最終階段產品:掩膜。

SoC是什麼?

SYSTEM ON a CHIP

3 EDA設計的流程

設計輸入(Design Entry)

-

分為兩種:

-

原理圖輸入(Schematic diagrams )

-

硬件描述語言(HDL文本 輸入)

-

VHDL

-

Verilog HDL

-

-

-

硬件描述語言與軟件編程語言(C、PASCAL等)有本質的區別

綜合(Synthesis)

將較高層次的設計描述自動轉化為較低層次描述的過程。

-

行為綜合:從算法表示、行為描述->寄存器傳輸級(RTL)

-

邏輯綜合:RTL級描述->邏輯門級(包括觸發器)

-

版圖綜合或結構綜合:從邏輯門表示->版圖表示,或->PLD器件的配置網表表示

綜合器是能夠自動實現上述轉換的軟件工具,是能將原理圖或HDL語言描述的電路功能轉化為具體電路結構網表的工具

綜合 這個概念在硬件里相當於軟件的編譯。

軟件編譯器和硬件綜合器有所差別:

軟件編譯(Compiler)->CPU指令/數據代碼(01碼)

硬件綜合(synthesizer)->為ASIC設計提供電路網表文件

適配

適配器也稱為結構綜合器。

它的功能是將由綜合器產生的網表文件配置於指定的目標器件中,併產生最終的可下載文件。

對CPLD器件而言,產生熔絲圖文件,即JEDEC文件;

對FPGA器件則產生Bitstream位流數據文件。

仿真

仿真是對所設計電路的功能的驗證。

-

功能仿真(Function Simulation)

-

時序仿真(Timing Simulation)

編程(下載/配置)

把適配後生成的編程文件裝入到PLD器件(可編程邏輯器件)中的過程, 或稱為下載。

通常將對基於EEPROM工藝的非易失結構PLD器件的下載稱為編程(Program);

將基於SRAM工藝結構的PLD器件的下載稱為配置(Configure)。

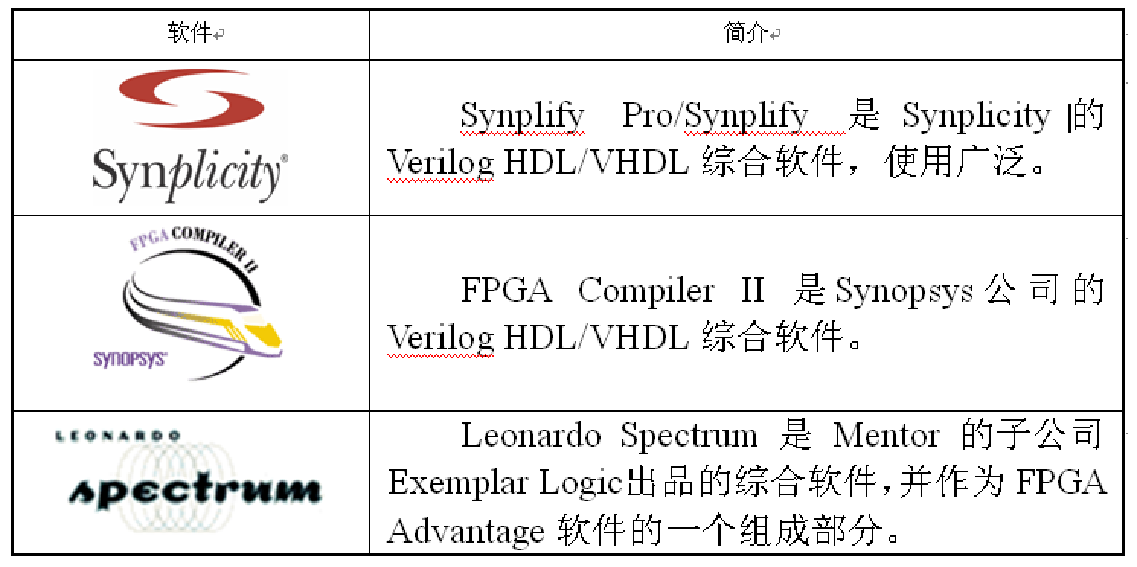

4 常用的EDA軟件工具

-

集成的CPLD/FPGA開發工具

-

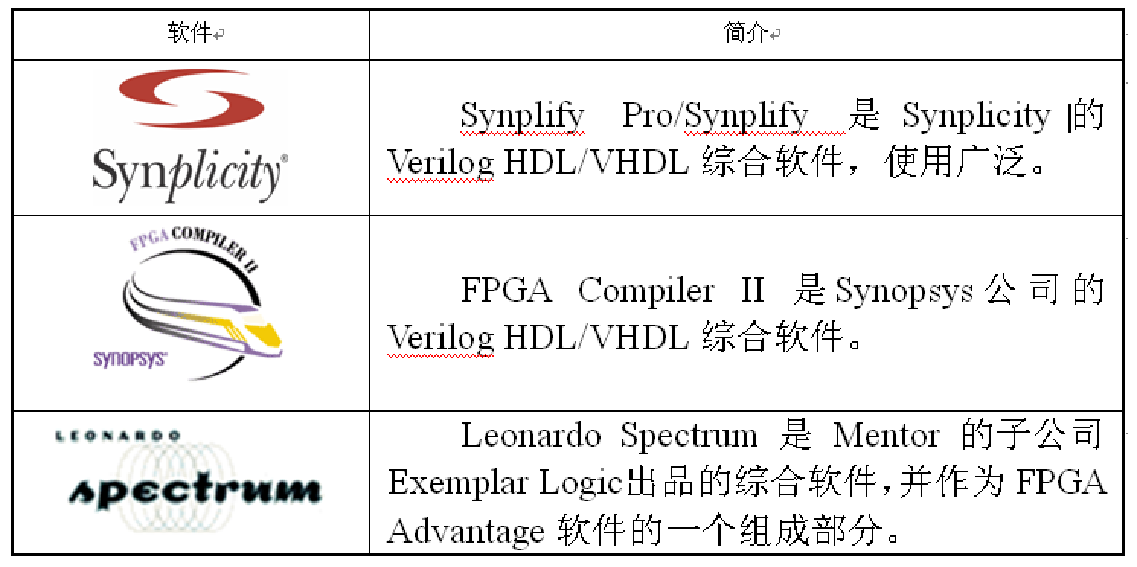

邏輯綜合工具

-

仿真工具

-

其他設計工具

5 EDA技術的發展趨勢

-

超大規模集成電路的集成度和工藝水平不斷提高。

-

市場對系統的集成度不斷提出更高的要求。

-

高性能的EDA工具,其自動化和智能化程度不斷提高,為嵌入式系統設計提供了功能強大的開發環境。

-

計算機硬件平台性能大幅度提高,為複雜的SoC設計提供了物理基礎。