【計算機組成原理】第4章 存儲器

教材基於《計算機組成原理 第3版》 ——唐朔飛

存儲器

存儲器分類

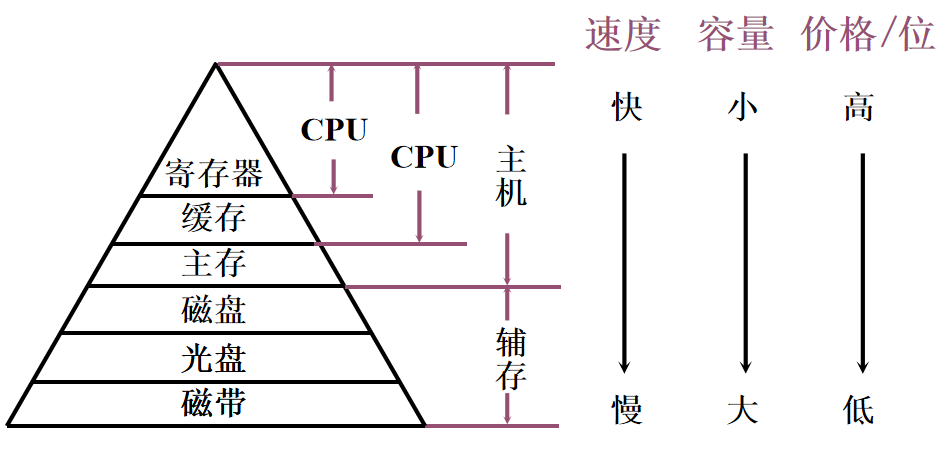

存儲器的層次結構

存儲器三個主要特性的關係

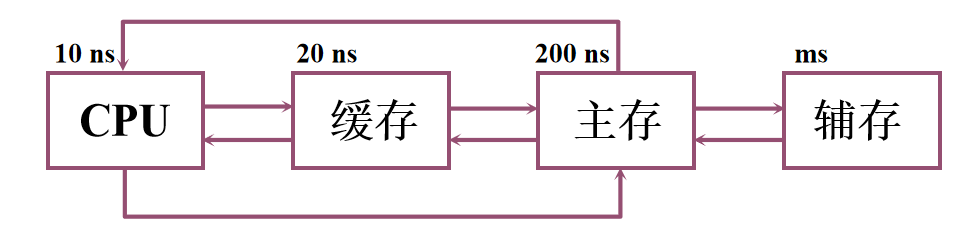

緩存——主存層次和主存——輔存層次

1️⃣ 緩存——主存層次主要解決CPU和主存速度不匹配的問題

2️⃣ 主存——輔存主要解決存儲系統的容量問題

3️⃣ 主存——輔存層次發展形成虛擬存儲系統。

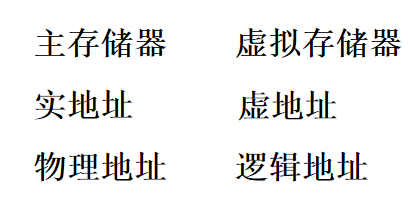

主存儲器

概述

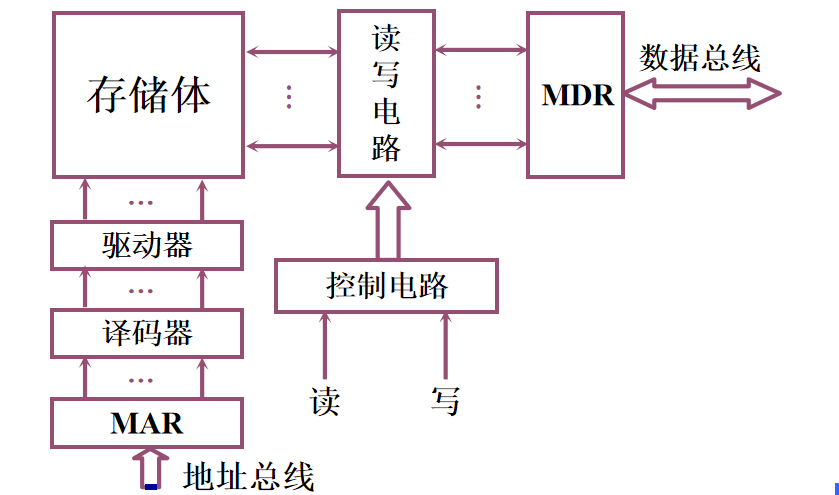

主存的基本組成

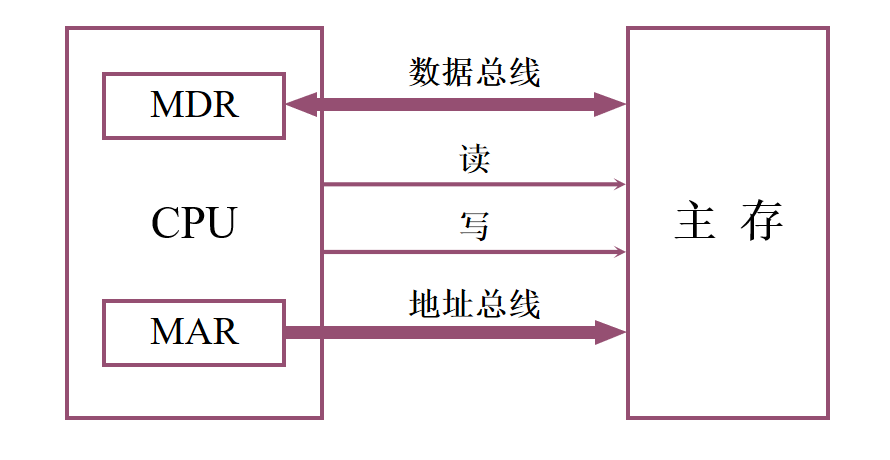

主存和CPU的聯繫

1️⃣ 驅動器、譯碼器和讀寫電路在存儲芯片中

2️⃣ MAR和MDR在CPU芯片中

3️⃣ 存儲芯片和CPU芯片可通過總線連接

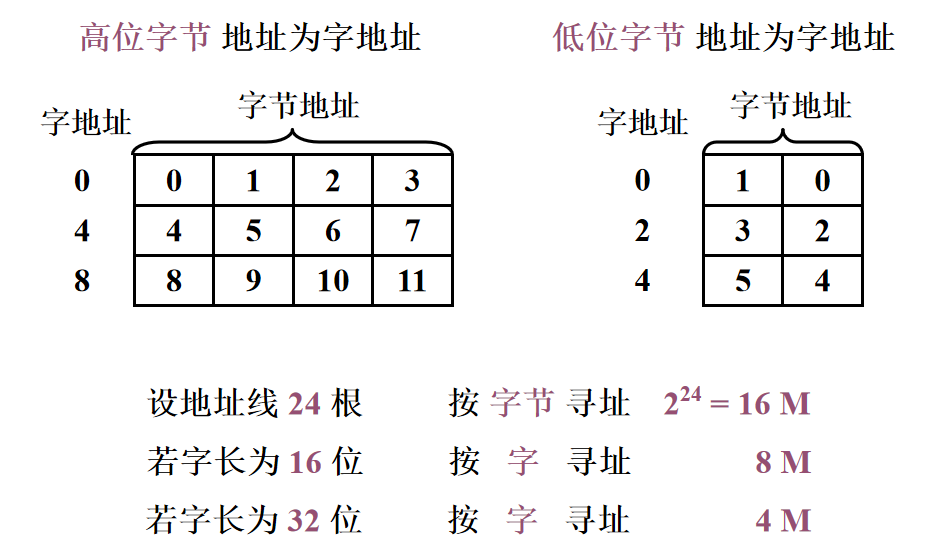

主存中存儲單元地址的分配

主存的技術指標

1️⃣ 存儲容量:主存存放二進制代碼的總位數,存儲容量(位)=存儲單元個數*存儲字長,存儲容量(位元組)=存儲單元個數*存儲字長 / 8

2️⃣ 存儲速度

- 存取時間:存儲器的訪問時間=讀出時間+寫入時間

- 存取周期:連續兩次獨立的存儲器操作(讀或寫)所需的 最小間隔時間

3️⃣ 存儲器的帶寬:單位時間內存儲器存取的信息量,每個存儲周期可以訪問的位(位元組)數 / 存儲周期

提高存儲器帶寬的措施

- 縮短存儲周期

- 增加存儲字長

- 增加存儲體

半導體存儲芯片簡介

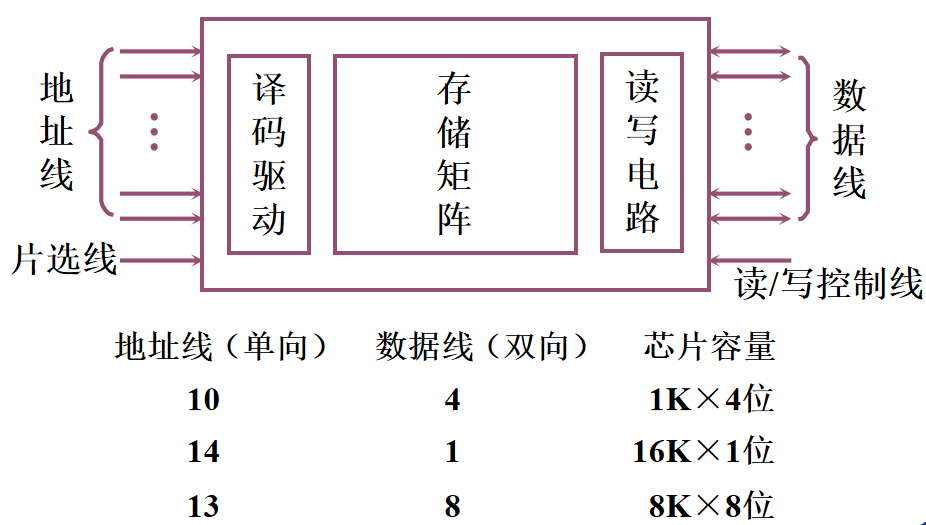

半導體存儲芯片的基本結構

1️⃣ 地址線:單向輸入,位數與存儲字的個數有關

2️⃣ 數據線:雙向的,位數與讀/寫的數據位數有關

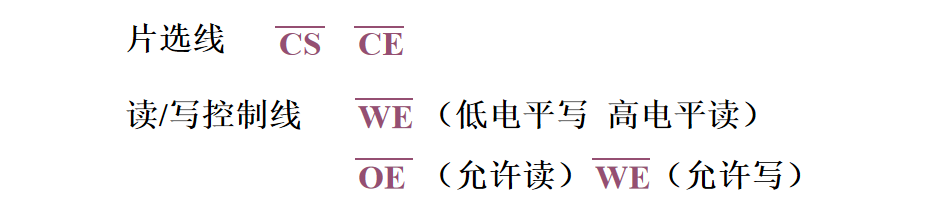

3️⃣ 控制線

- 讀/寫控制線:決定芯片進行讀/寫操作

- 片選線:選擇存儲芯片

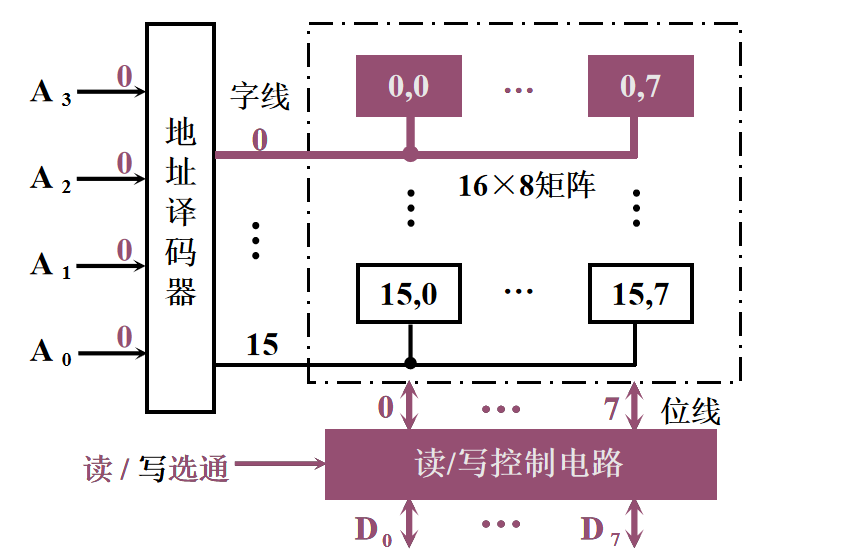

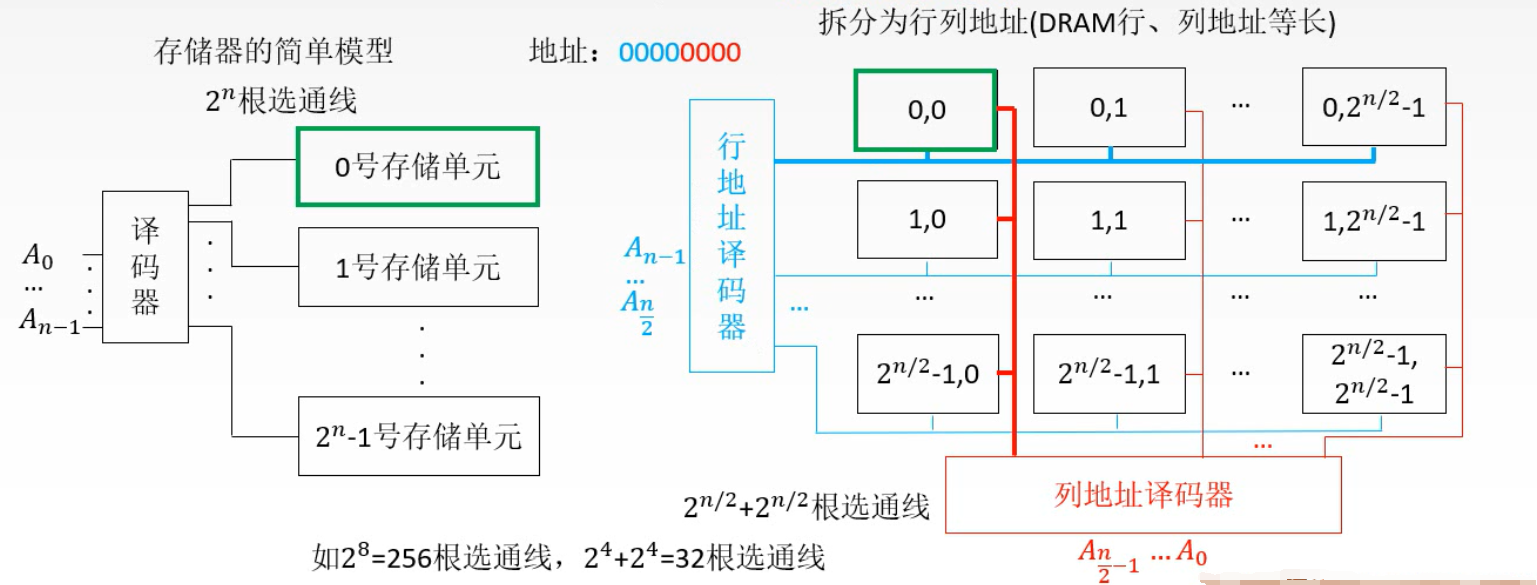

半導體存儲芯片的譯碼驅動方式

🌈 線選法

1️⃣ 特點:一根字選擇線(字線),直接選中一個存儲單元的各位

2️⃣ 結構簡單,只適於容量不大的存儲芯片

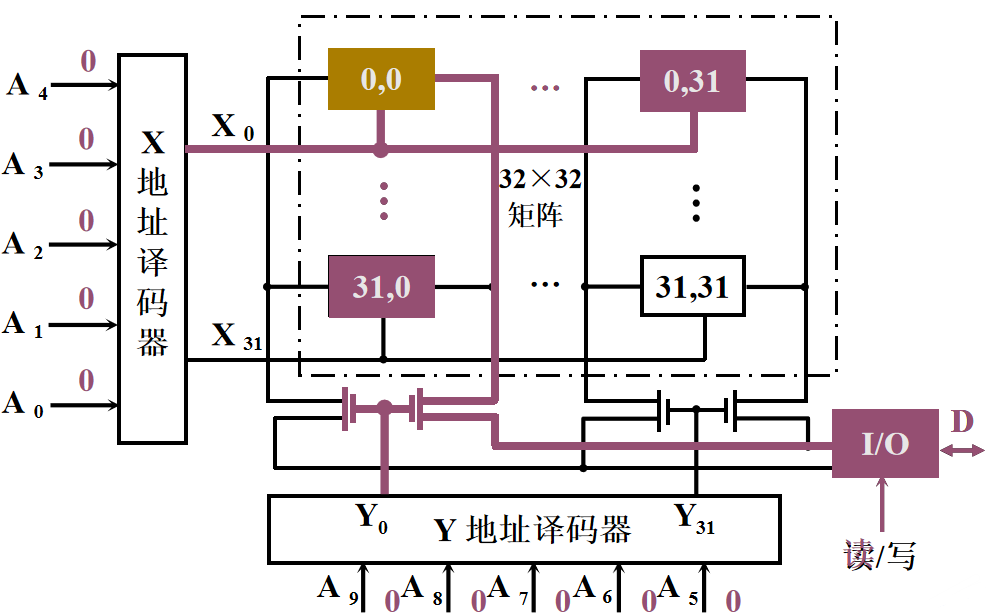

🌈 重合法

1️⃣ 特點:被選單元是由X、Y兩個方向的地址決定的

2️⃣ 適合容量較大的存儲芯片

隨機存取存儲器 ( RAM )

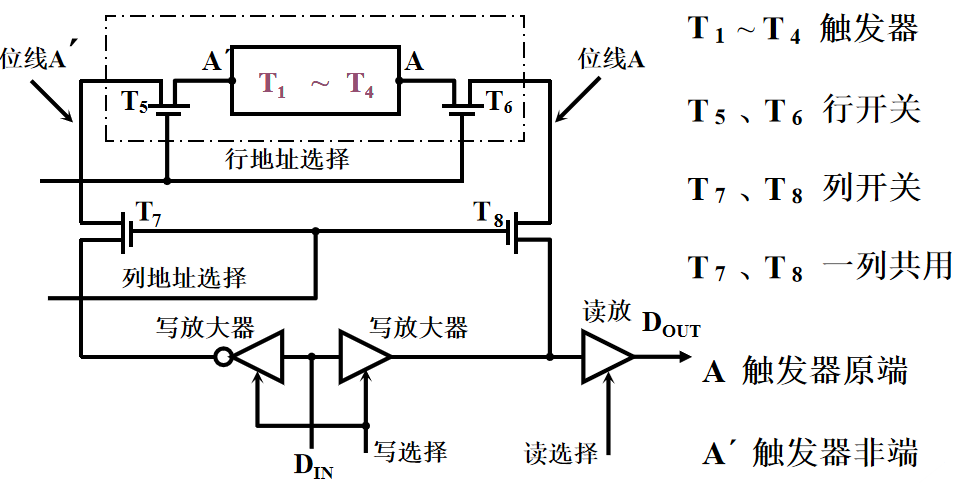

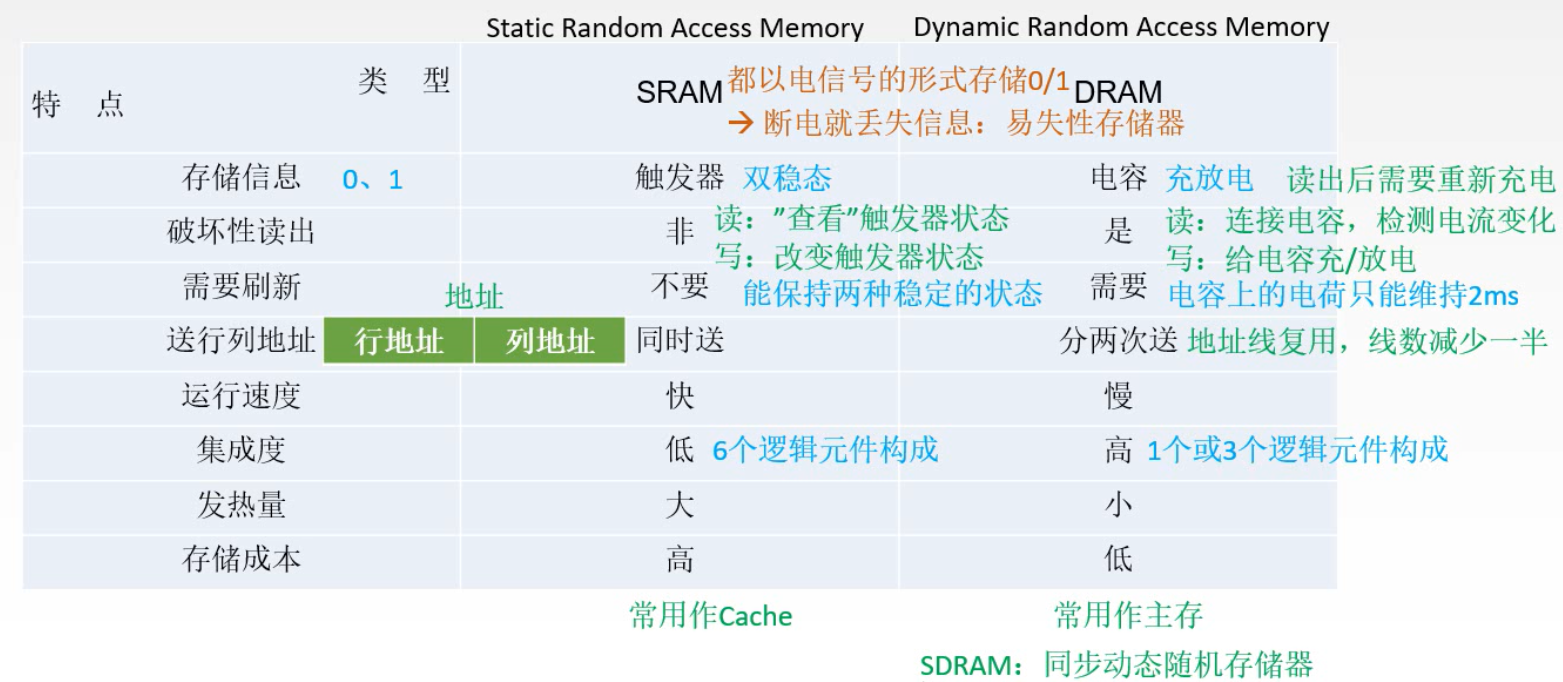

靜態 RAM (SRAM)

基本電路

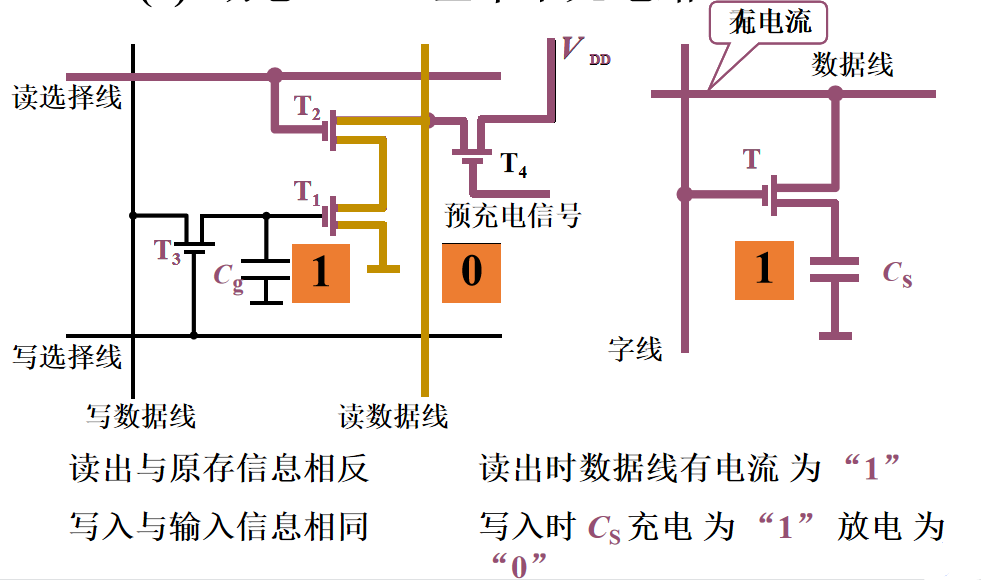

動態 RAM ( DRAM )

基本電路

動態 RAM 刷新

1️⃣ 多久需要刷新一次:刷新周期一般為 2 ms

2️⃣ 每次刷新多少存儲單元:以行為單位,每次刷新一行存儲單元

————為什麼要使用行列地址:減少選通線的數量

3️⃣ 如何刷新:有硬件支持,讀出一行的信息後重新寫入,佔用1個讀/寫周期

4️⃣ 在什麼時候刷新:

動態 RAM 和靜態 RAM 的比較

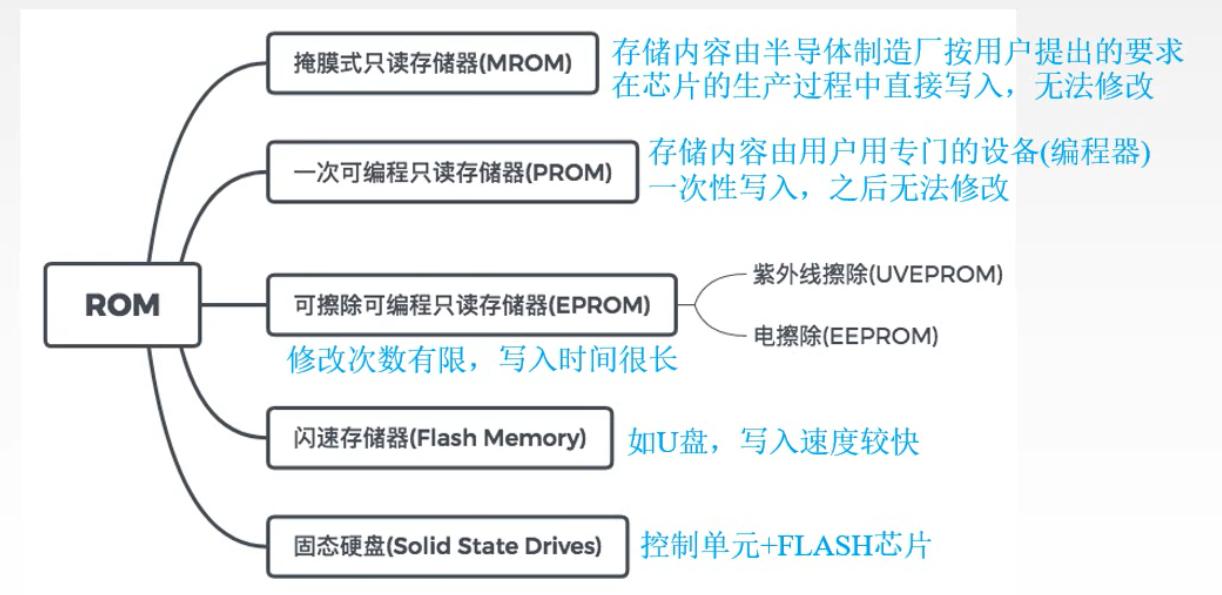

只讀存儲器(ROM)

存儲器與 CPU 的連接

存儲器容量的擴展

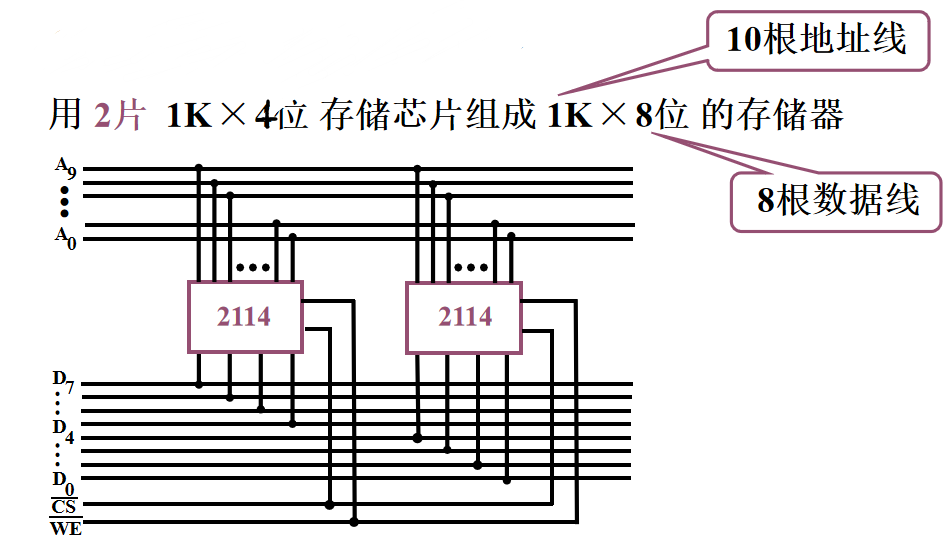

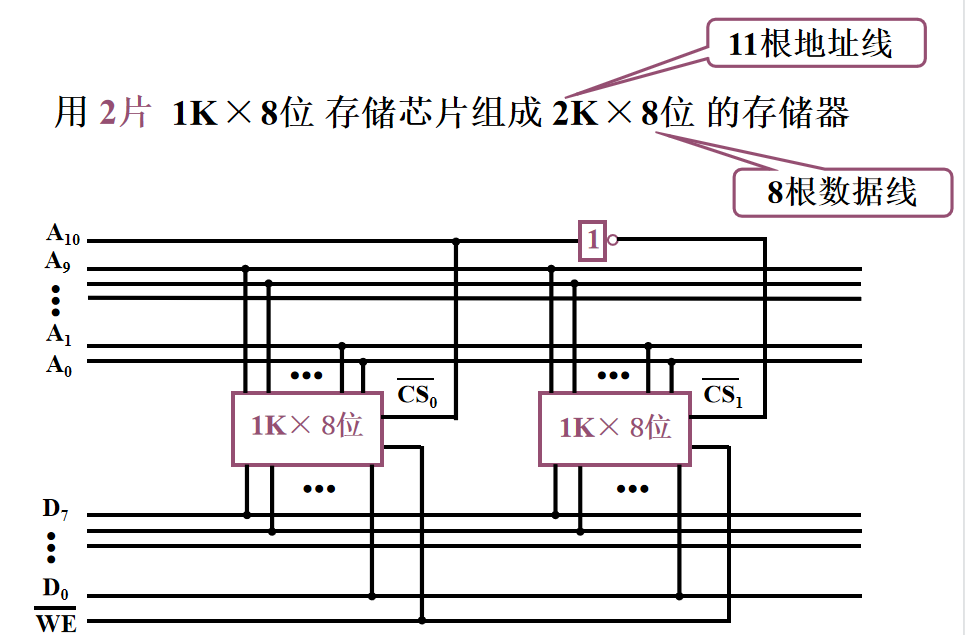

位擴展(增加存儲字長)

片選線相同,分配數據線

字擴展(增加存儲字的數量)

數據線相同,設置片選線

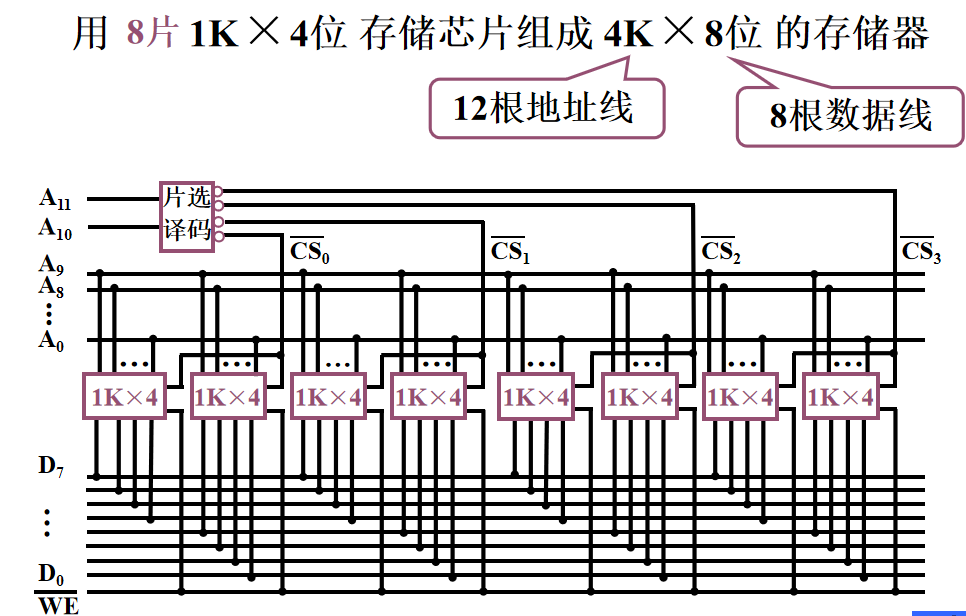

字、位同時擴展

數據線和片選線都要重新考慮

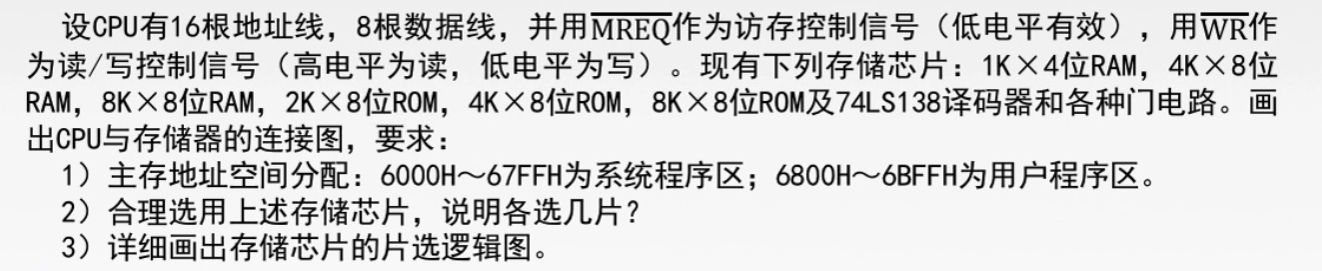

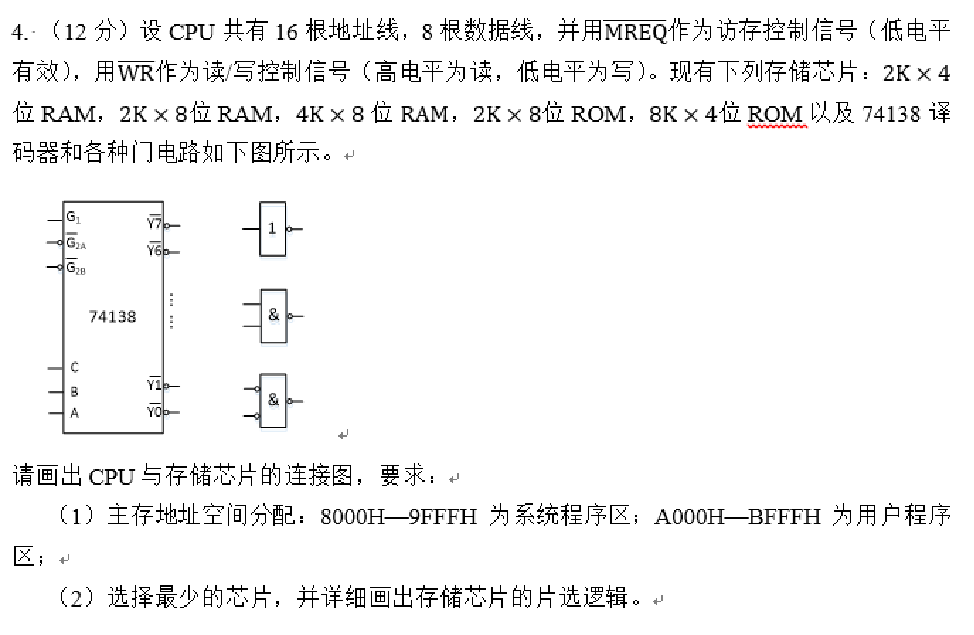

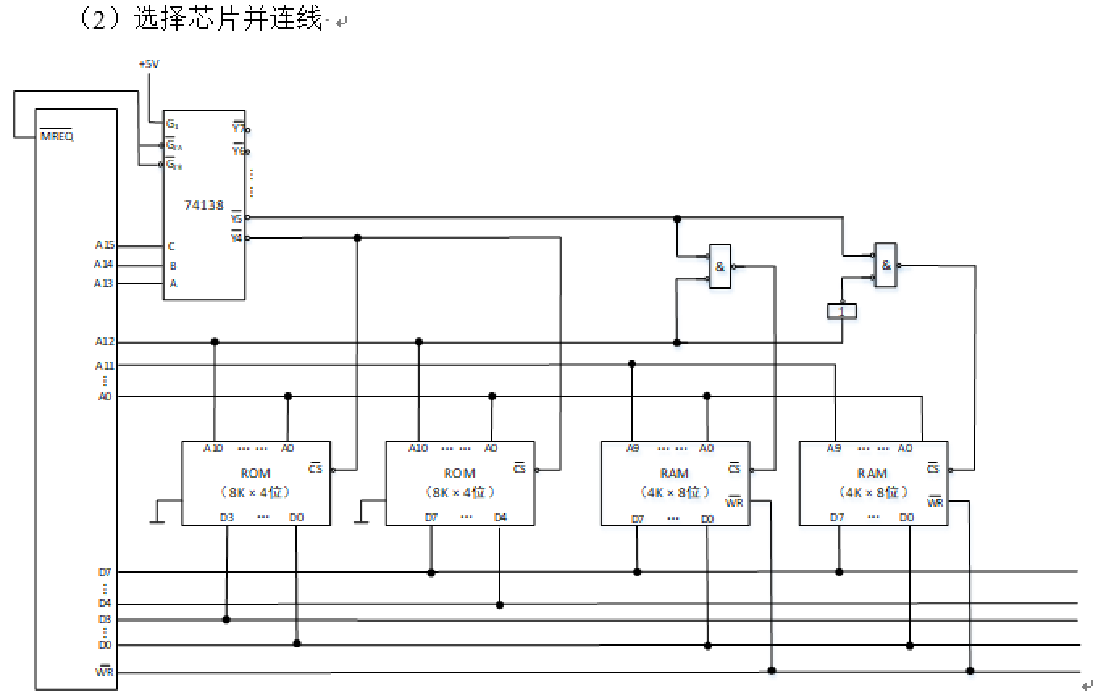

例題以及解題步驟

🔔 系統程序區用ROM,用戶程序區用RAM

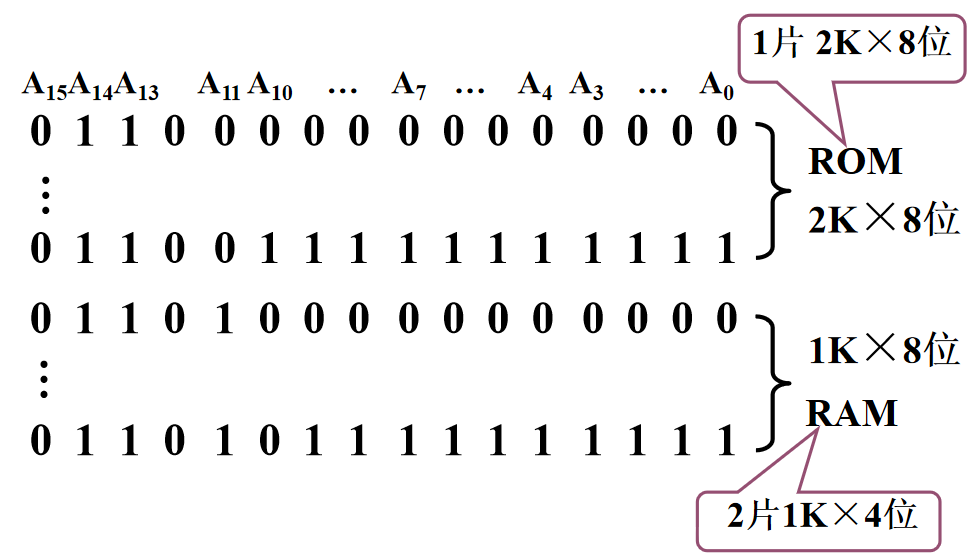

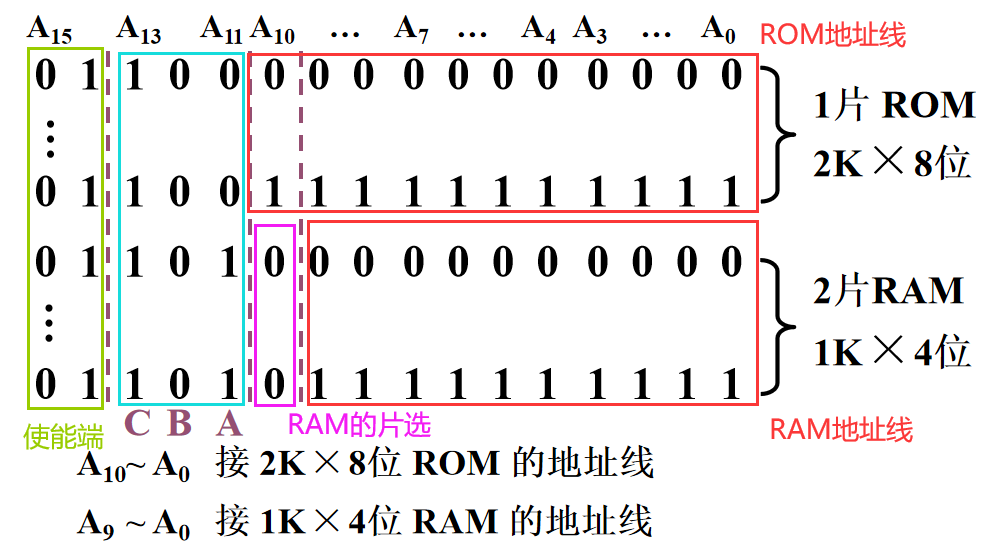

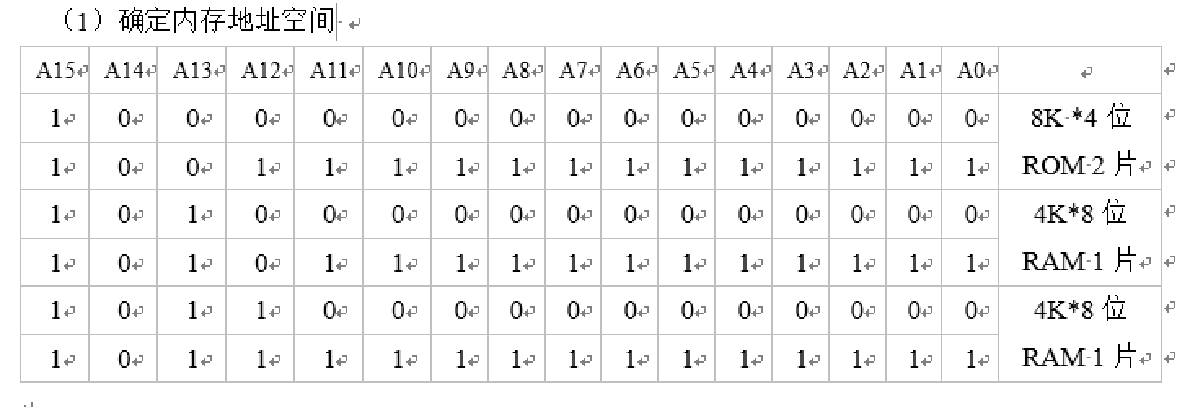

1️⃣ 寫出對應的二進制地址碼

2️⃣ 確定芯片的數量及類型

由題目知 CPU 數據線8根,則存儲器位數應擴展為8位。再根據題目所給的存儲芯片

系統程序區選擇一片 2 K * 8 位的存儲芯片

用戶程序區選擇兩片 1 K * 4 位的存儲芯片

3️⃣ 分配地址線

4️⃣ 確定片選信號

RAM 是位拓展,共享片選線,分配數據線

而 ROM 和 RAM 需要考慮片選線的設置

譯碼器的 Y4 端可以作為 ROM 的片選線端口

譯碼器的 Y5 端和 RAM 的 A10 地址線可以聯合作為 RAM 的片選控制

🔔 有一個默認的原則:不要有任何地址線空着不用!!!

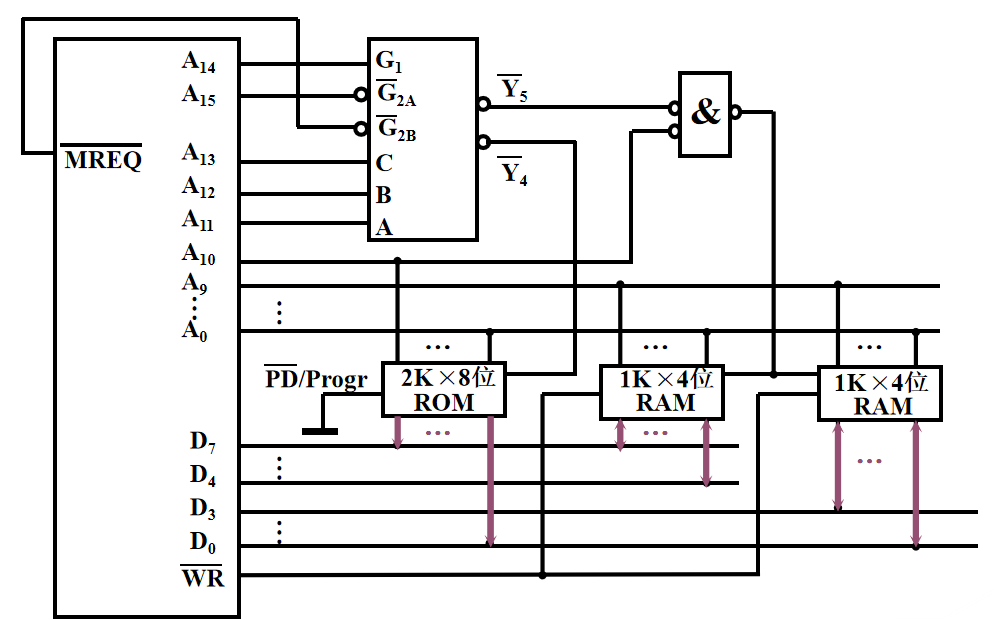

5️⃣ 連接圖

6️⃣ 注意的細節

ROM 要接地

與門都取了非,也就是說輸入的數據都為 0 時,輸出為 1

RAM 的地址線分配,RAM 要連接讀寫控制線 WR

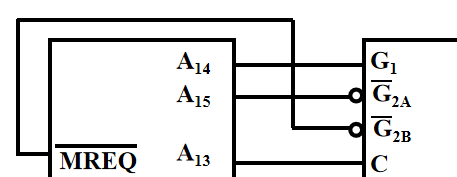

使能端只有輸入信號為 G1 G2A G2B: 1 0 0 時才工作

真題

該題與上一個題的區別就是 RAM 是字拓展而不是位拓展,所以數據線相同,片選線要配置,用 A12 作為劃分

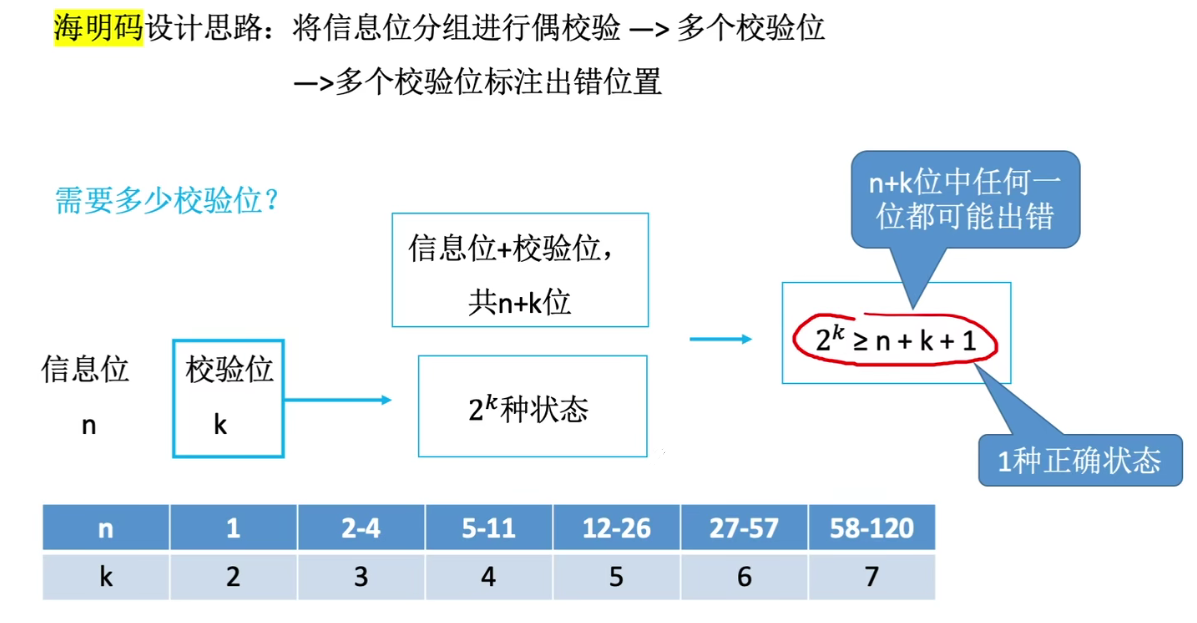

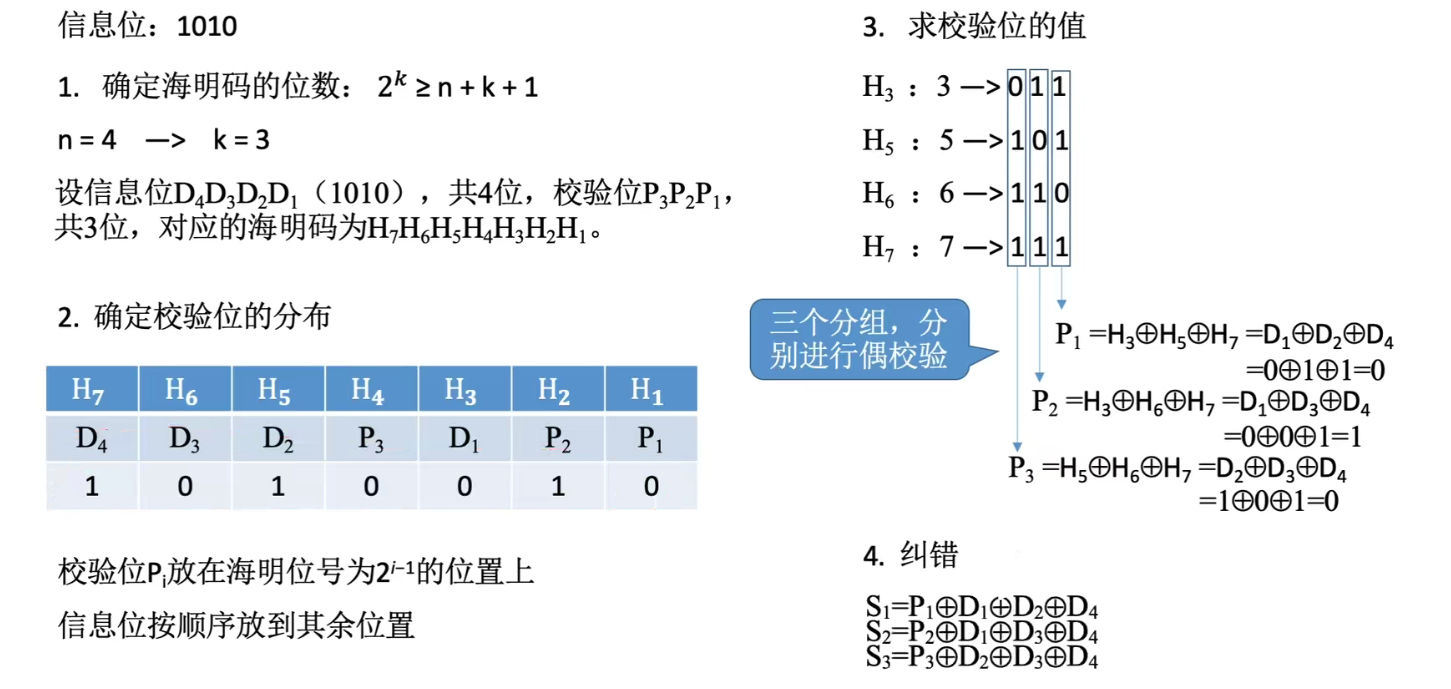

存儲器的校驗

海明碼

🔔 默認是偶校驗,如果題目要求是奇校驗,那不論是求海明碼還是糾錯,每個運算最後都要多異或一個 1 。

提高訪存速度的措施

-

採用高速器件

-

採用層次結構 Cache – 主存

-

調整主存結構

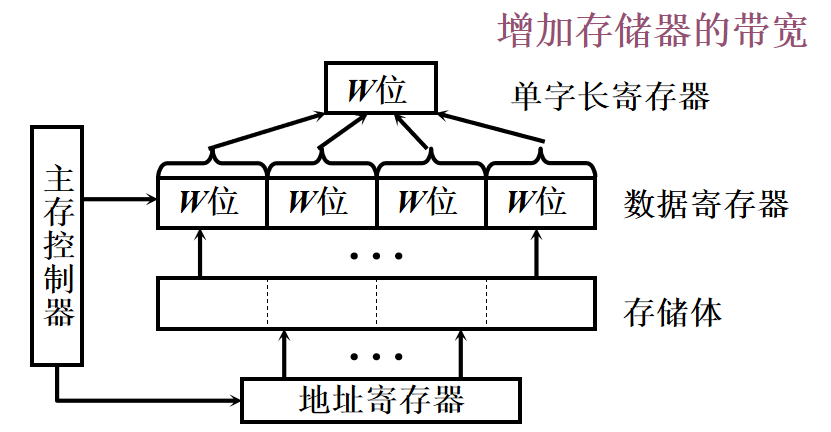

單體多字系統

普通存儲器:每行為一個存儲單元

🌈 單體多字存儲器

每個存儲單元存儲 m 個字,每個字 w 位,總線寬度為 m 個字。一個存取周期內可以讀出 m 個字,也就是 m * w 位的指令或數據,使主存帶寬提高到 m 倍

🔔 缺點:指令和數據在主存內必須是連續存放的,一旦遇到轉移指令,或者操作數不能連續存放,這種方法的效果就不明顯

多體並行系統

-

高位交叉(順序存儲)

-

存儲體的存儲單元通過地址的高位進行分組,高位地址相同的存儲單元屬於同一個存儲體

-

CPU 有較大概率需要連續訪問同一個存儲體,效率較低

-

-

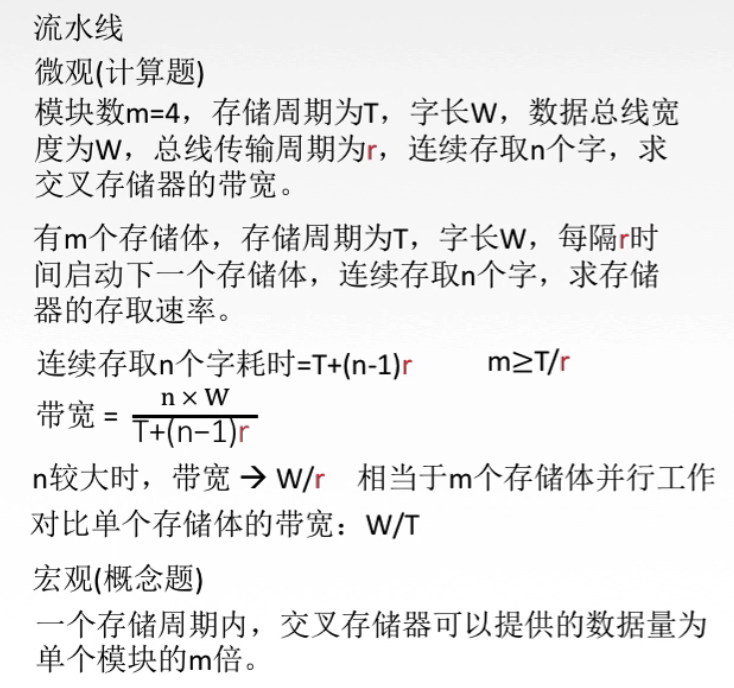

低位交叉(交叉存儲)

-

存儲體的存儲單元通過地址的低位進行分組,低位地址相同的存儲單元屬於同一個存儲體

-

CPU 可以較大概率同時訪問多個存儲體,效率高,屬於流水線方式

-

可以在不改變每個模塊存取周期的前提下,提高存儲器的帶寬

-

可以並行工作,如總線寬度為 mw 時,可以同時取出長度為 mw 的數據。等同於高位交叉存儲方式的 m 個存儲體並行工作

-

流水線的概念

例題

設有 4 個模塊組成的四體存儲器結構,每個體的存儲字長為 32 位,存儲周期為 200 ns。假設數據總線寬度為 32 位,總線傳輸周期為 50 ns,試求順序存儲和交叉存儲的存儲器帶寬。

解:順序存儲和交叉存儲連續讀出 4 個字的信息量是 32 * 4 = 128 位。

順序存儲器連續讀出 4 個字的時間是 200 ns * 4 = 800 ns

交叉存儲其連續讀出 4 個字的時間是 200 ns + 50 ns * (4 – 1) = 350 ns

順序存儲器的帶寬是 128 b / 800 ns = 16 * 10 ^ 7 bps

交叉存儲器的帶寬是 128 b / 350 ns = 37 * 10 ^ 7 bps

高速緩衝存儲器

概述

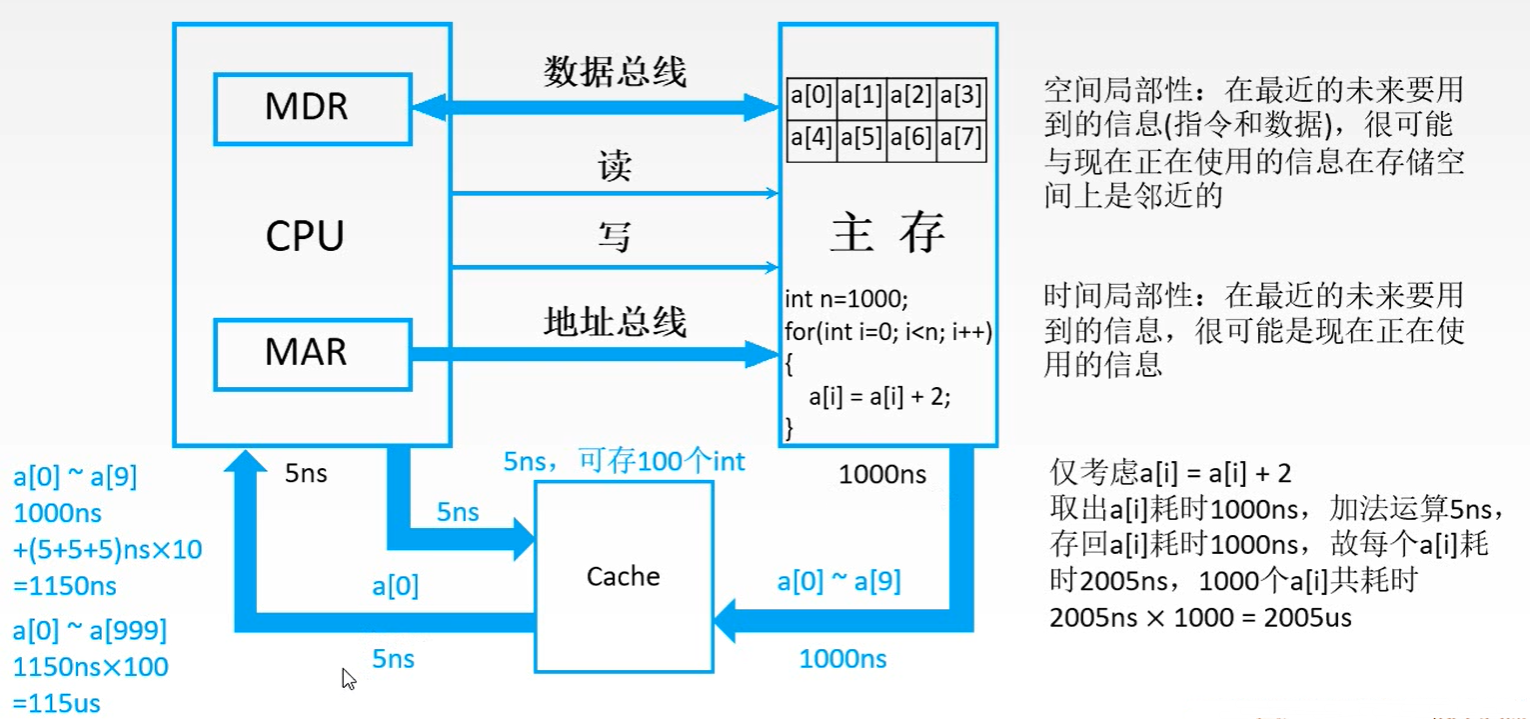

局部性原理

CPU 和主存(DRAM)的速度存在差異,為了避免 CPU 可能存在的「空等」現象

性能分析

1️⃣ 命中:

1.主存塊調入緩存

2.主存塊與緩存塊建立了對應關係

3.用標記記錄與某緩存塊建立了對應關係的主存塊號

2️⃣ 未命中:

1.主存塊未調入緩存

2.主存塊與緩存塊未建立對應關係

3️⃣ Cache 的命中率:

1.CPU 欲訪問的信息在 Cache 中的 比率

2.命中率 與 Cache 的 容量 與 塊長 有關

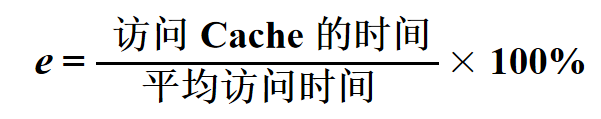

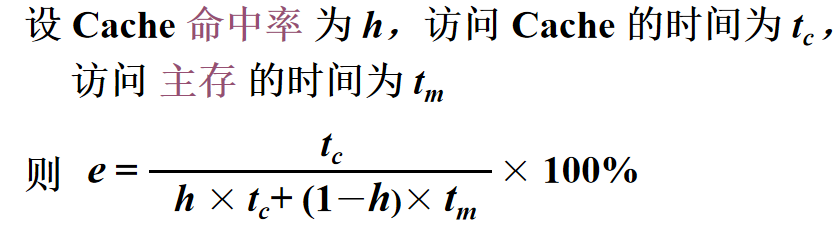

4️⃣ 主存系統的效率

1.效率 e 與 命中率 有關

🌈 例題

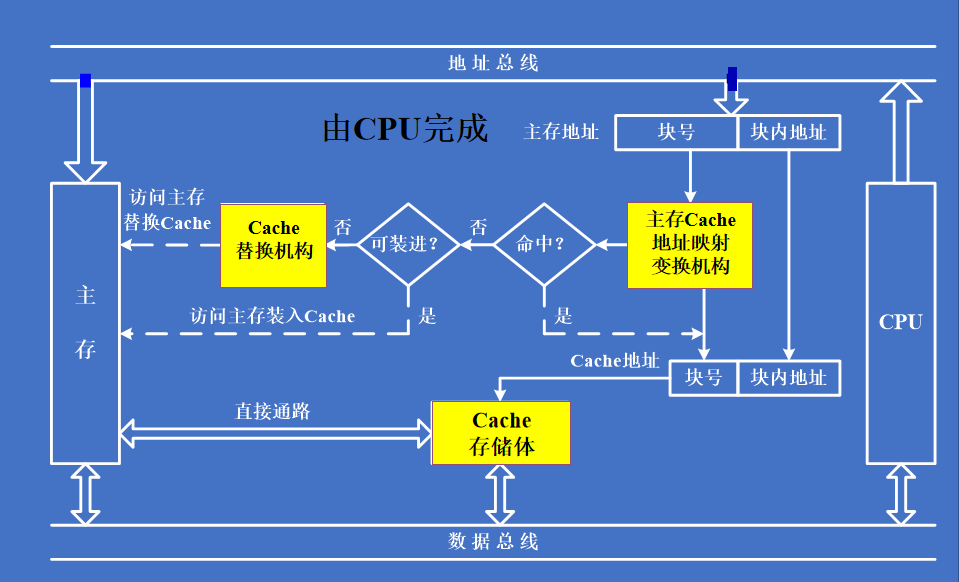

Cache 的基本結構

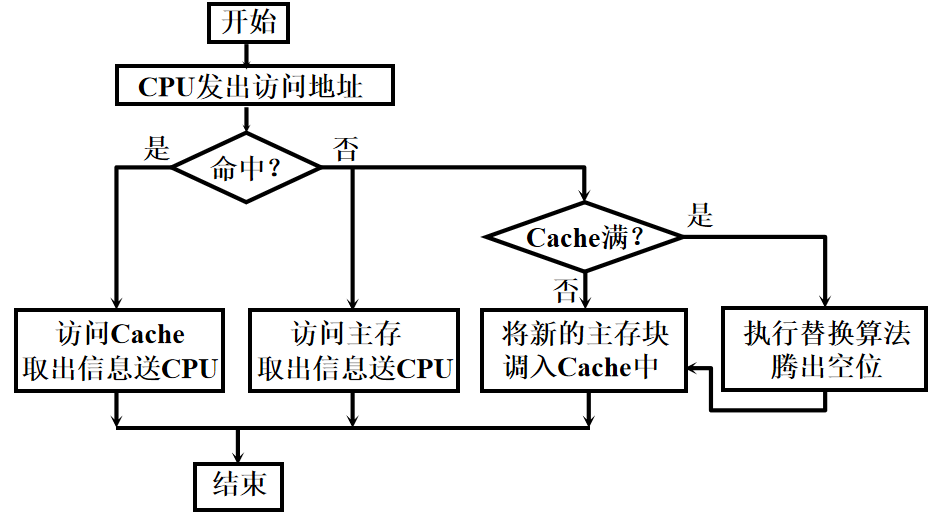

Cache 的讀寫操作

🌈 讀

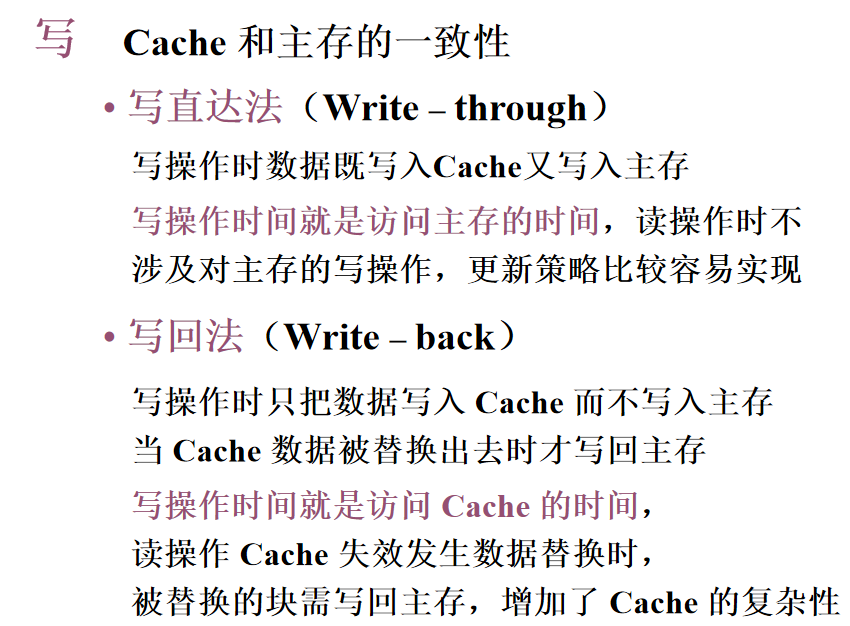

🌈 寫

Cache 的改進

1️⃣ 單一緩存和二級緩存

2️⃣ 統一緩存和分立緩存

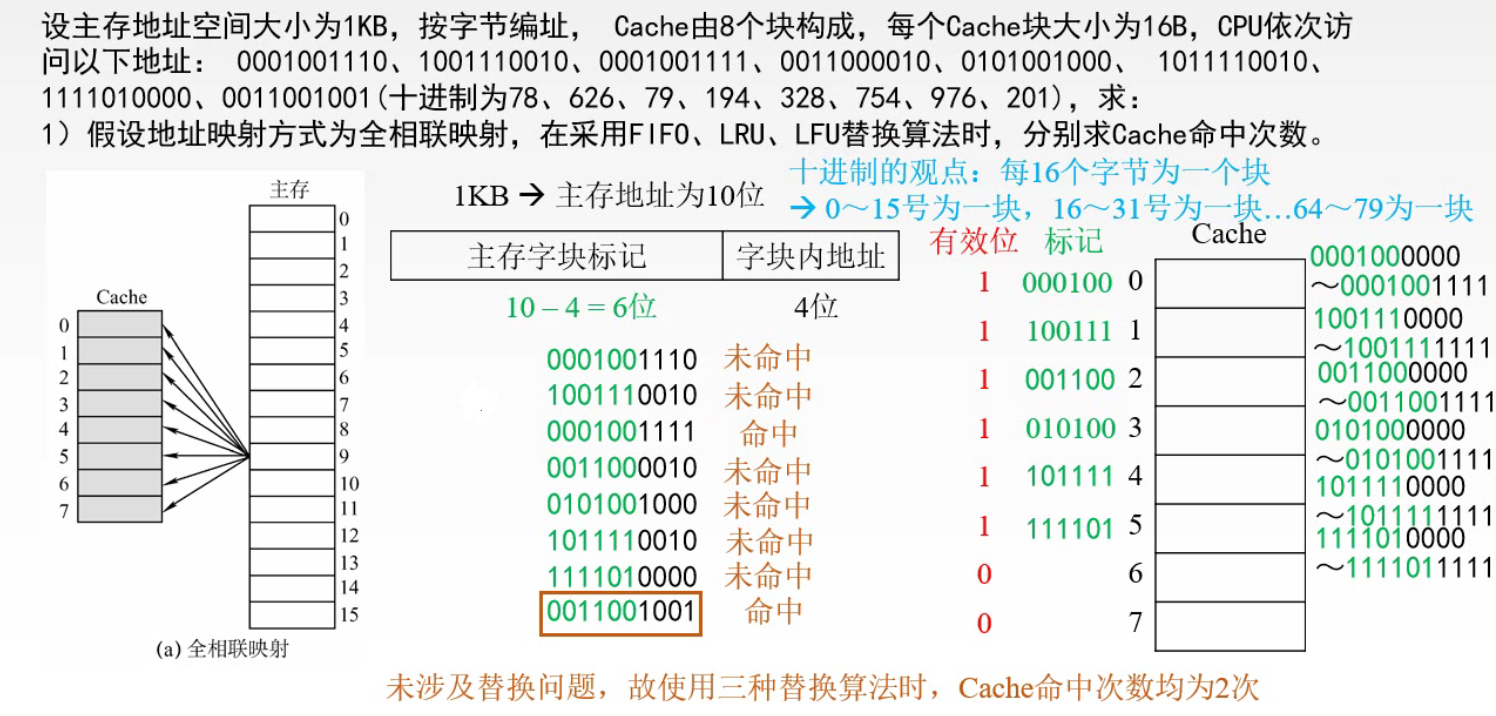

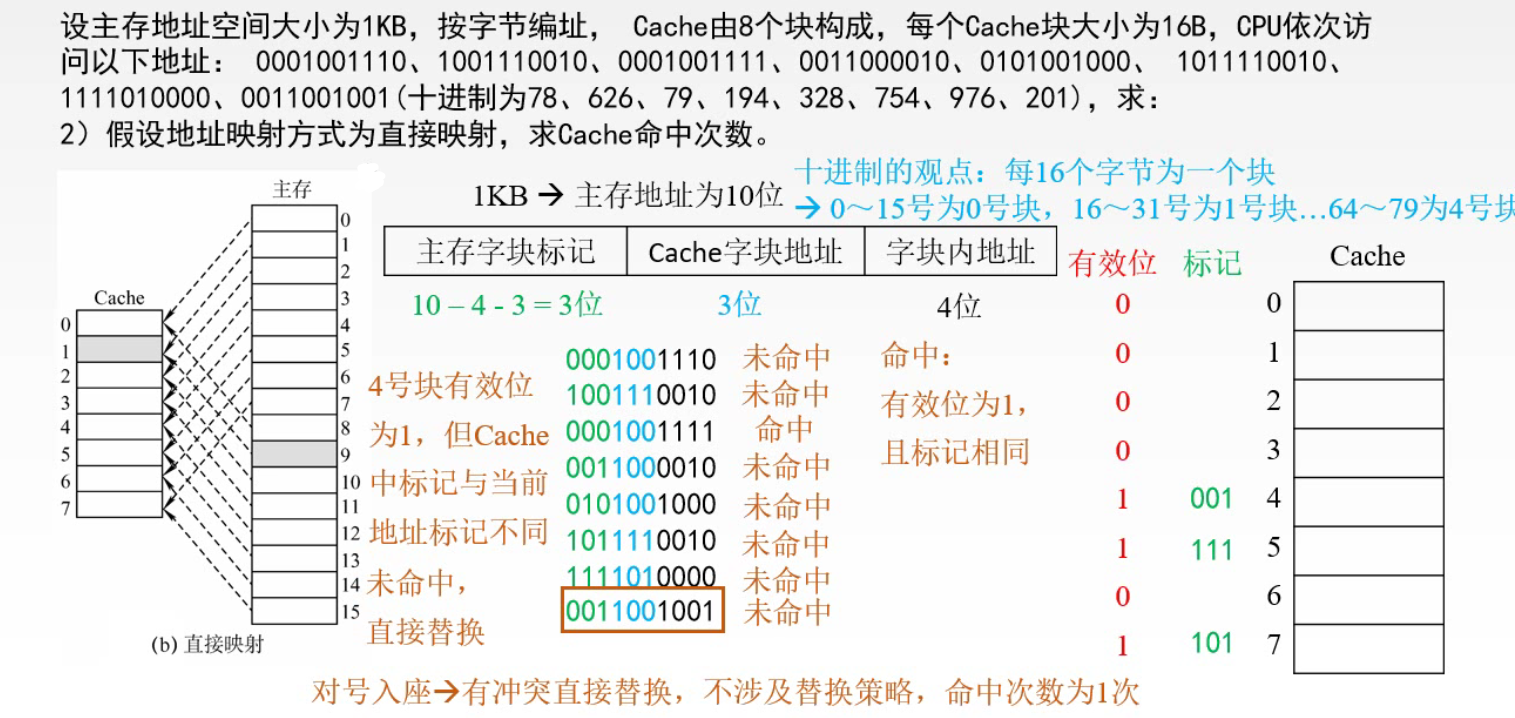

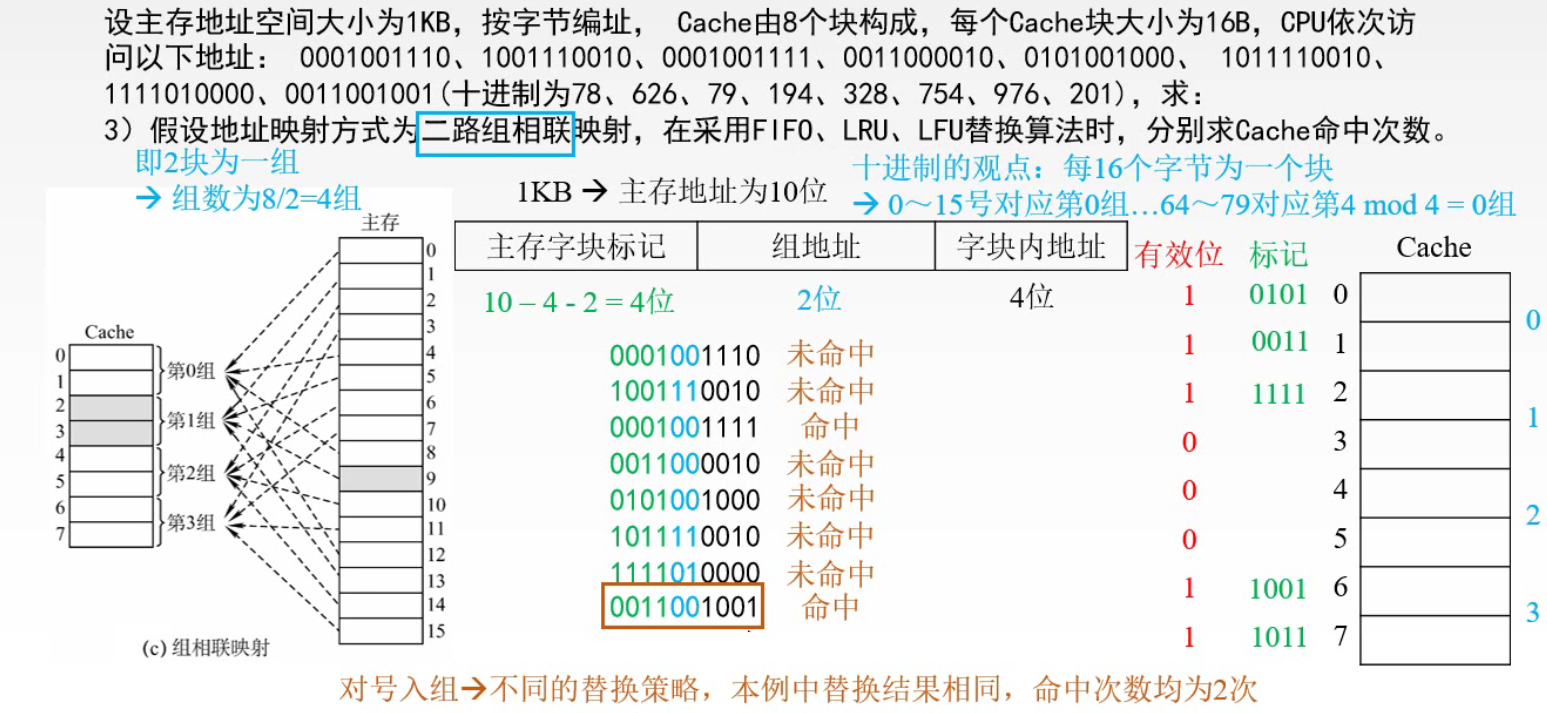

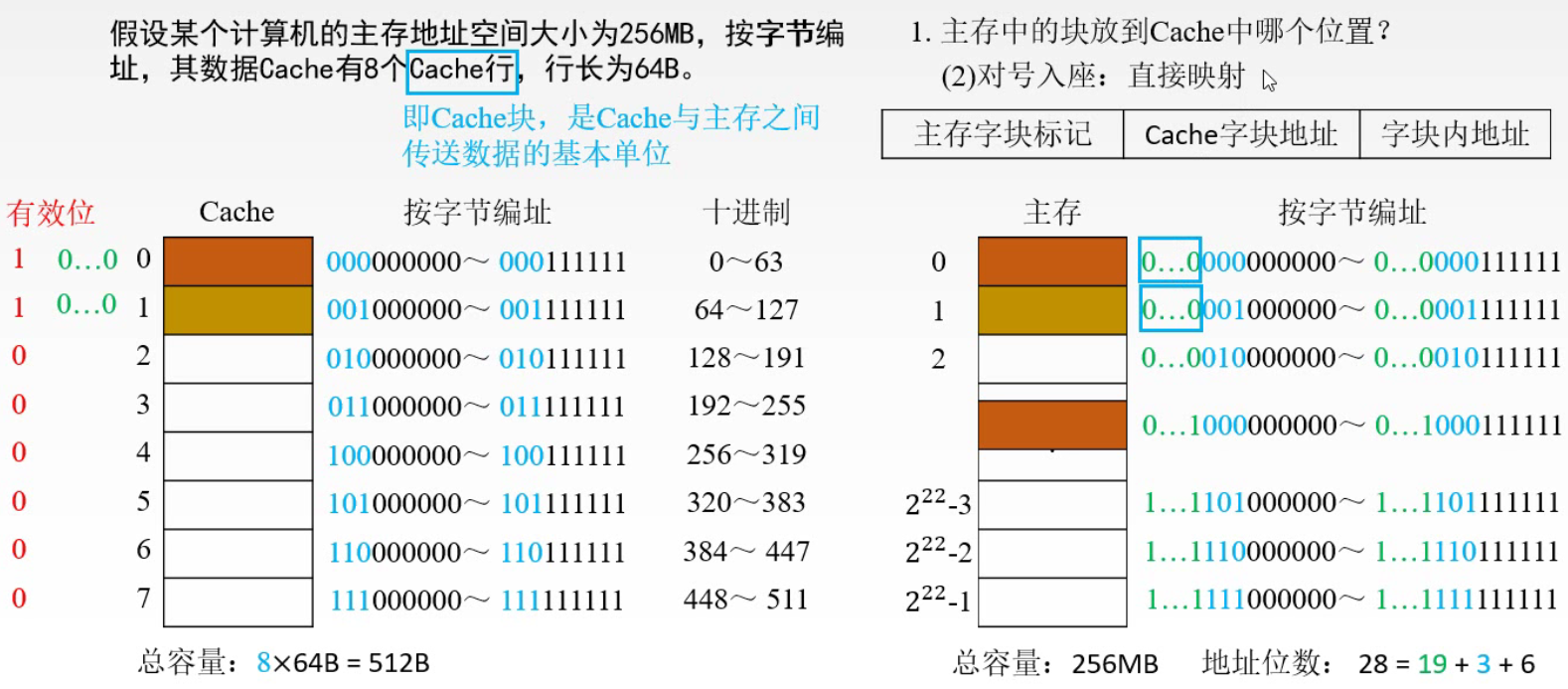

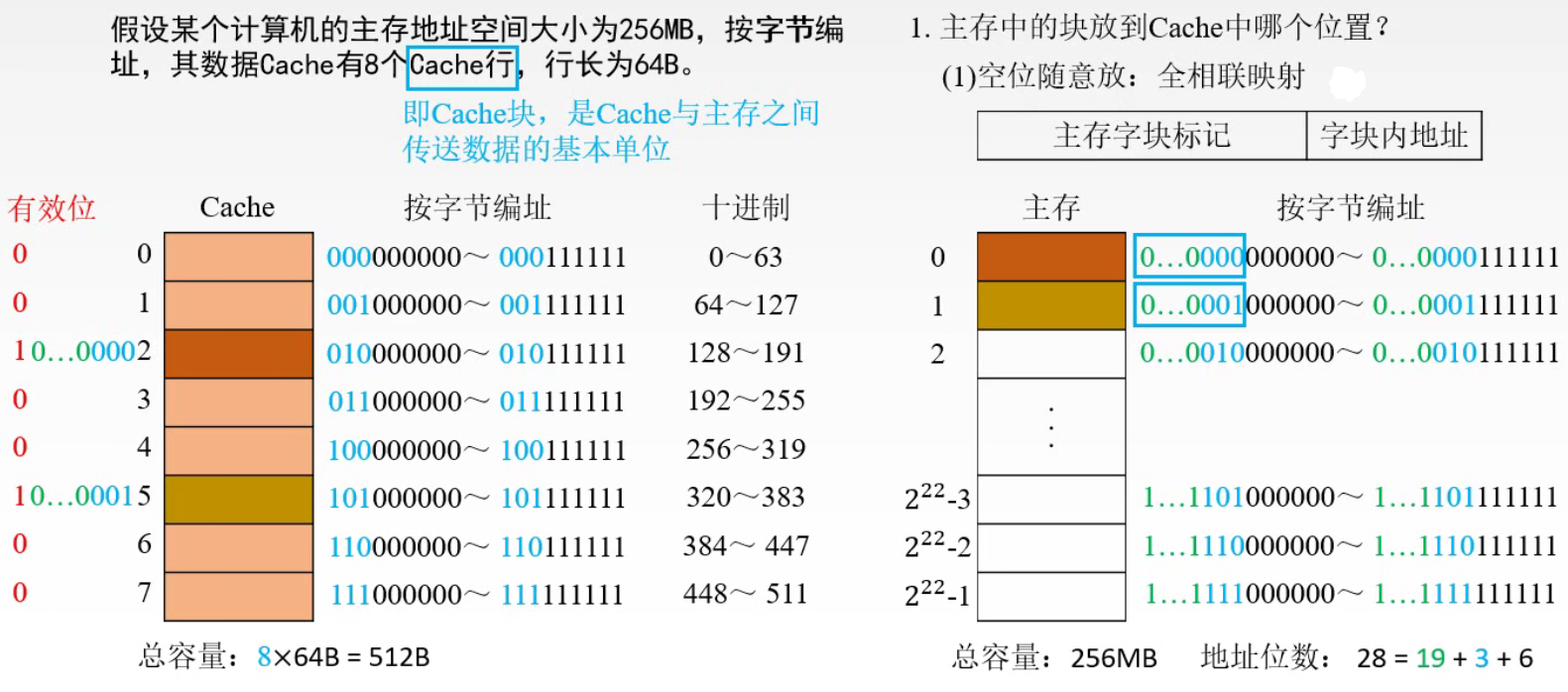

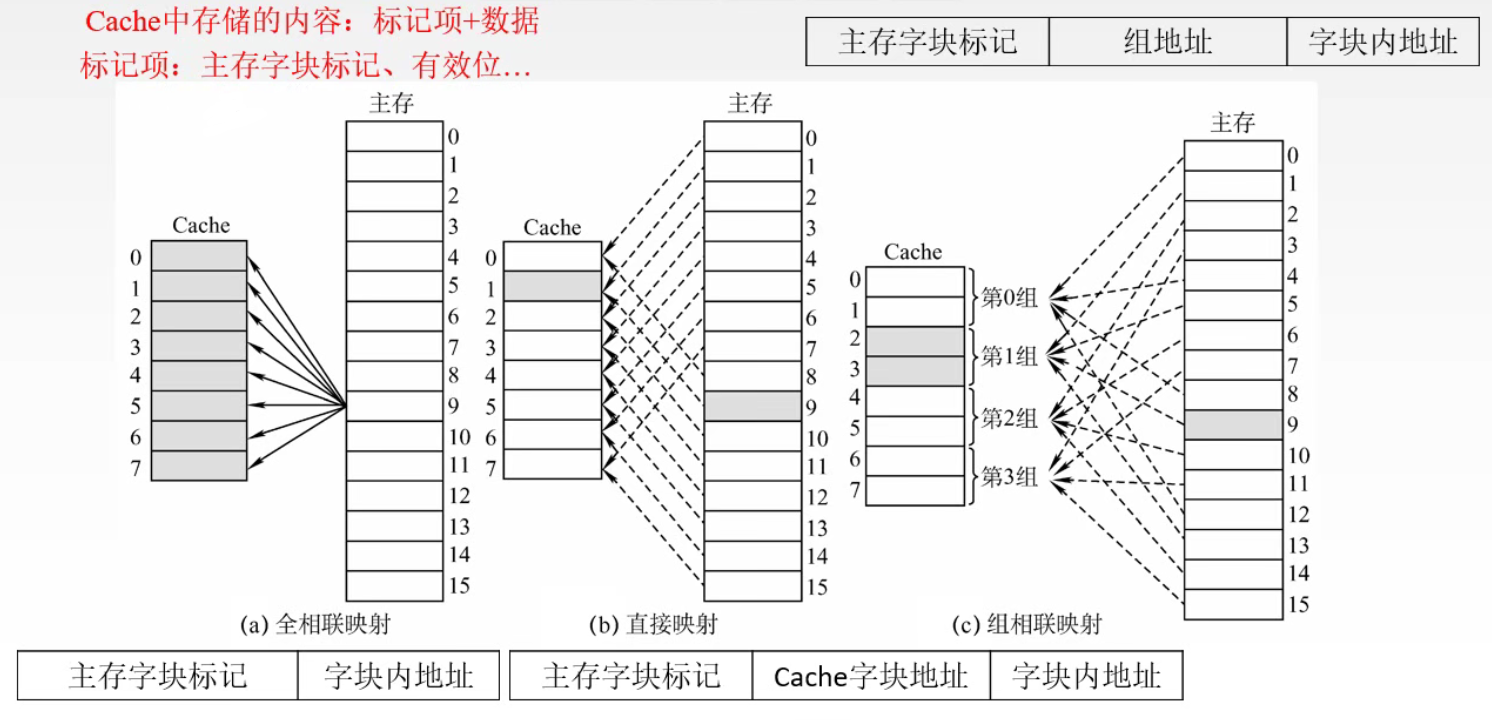

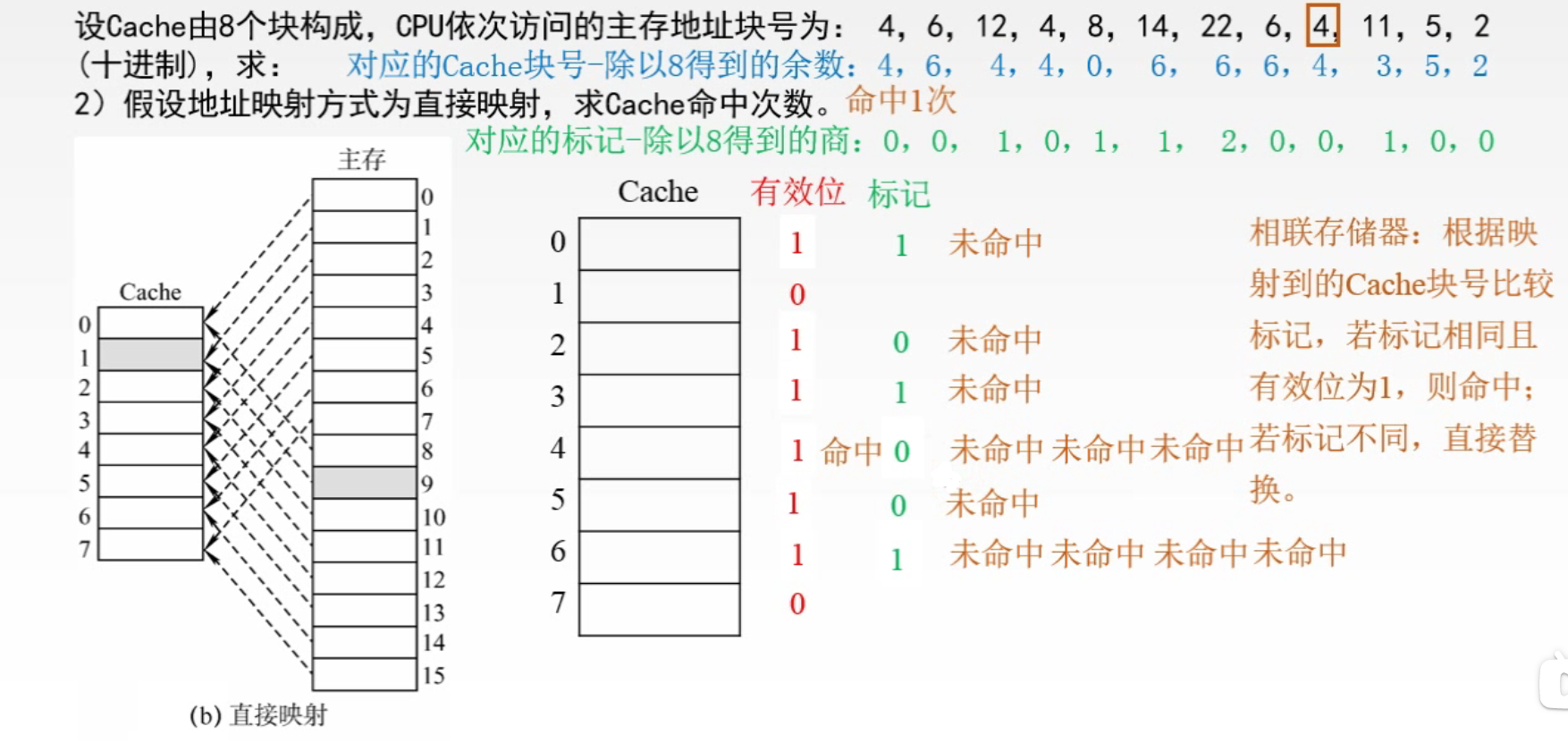

Cache – 主存的地址映射

直接映射

1️⃣ 每個緩存塊 i 可以和若干個主存塊對應

2️⃣ 每個主存塊 j 只能和一個緩存塊對應

3️⃣ i = j mod C (C 是 Cache 塊總數)

全相聯映射

主存中的任一塊可以映射到緩存中的任一塊

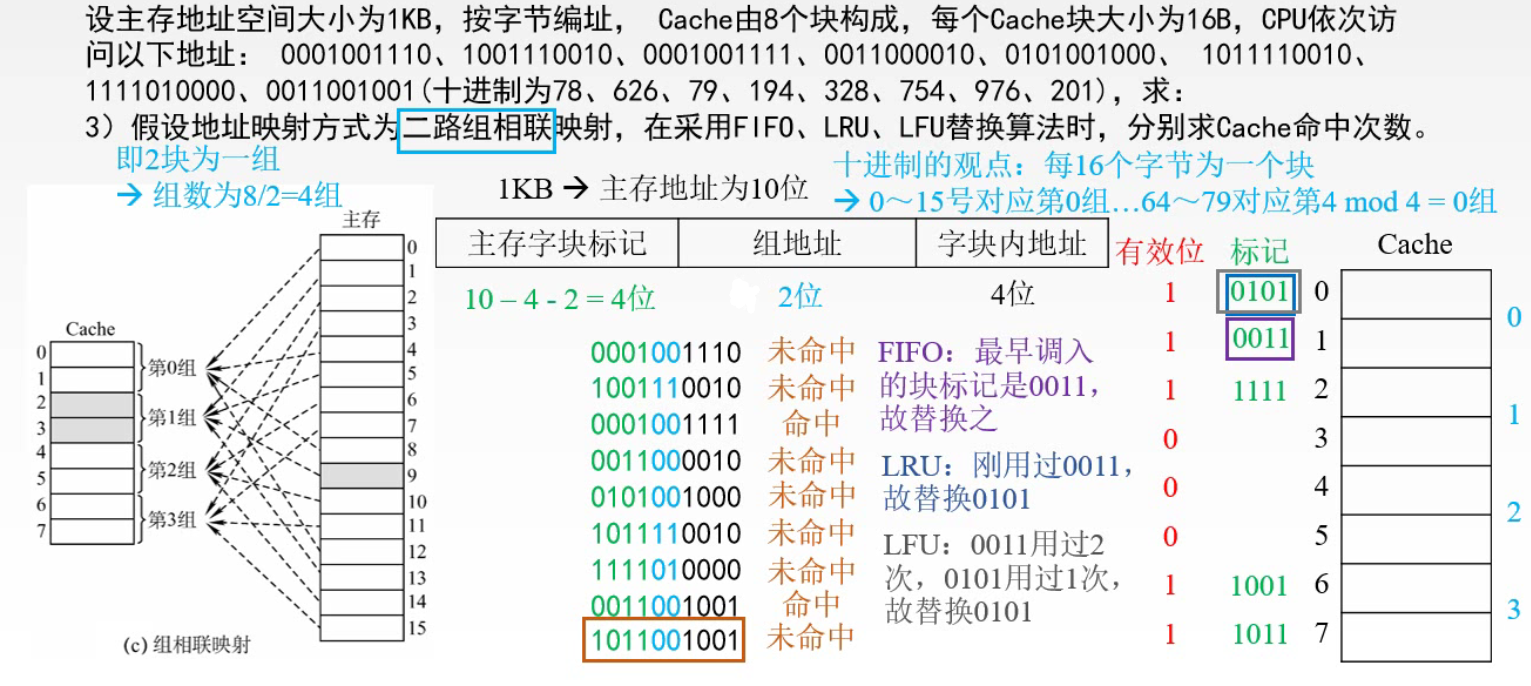

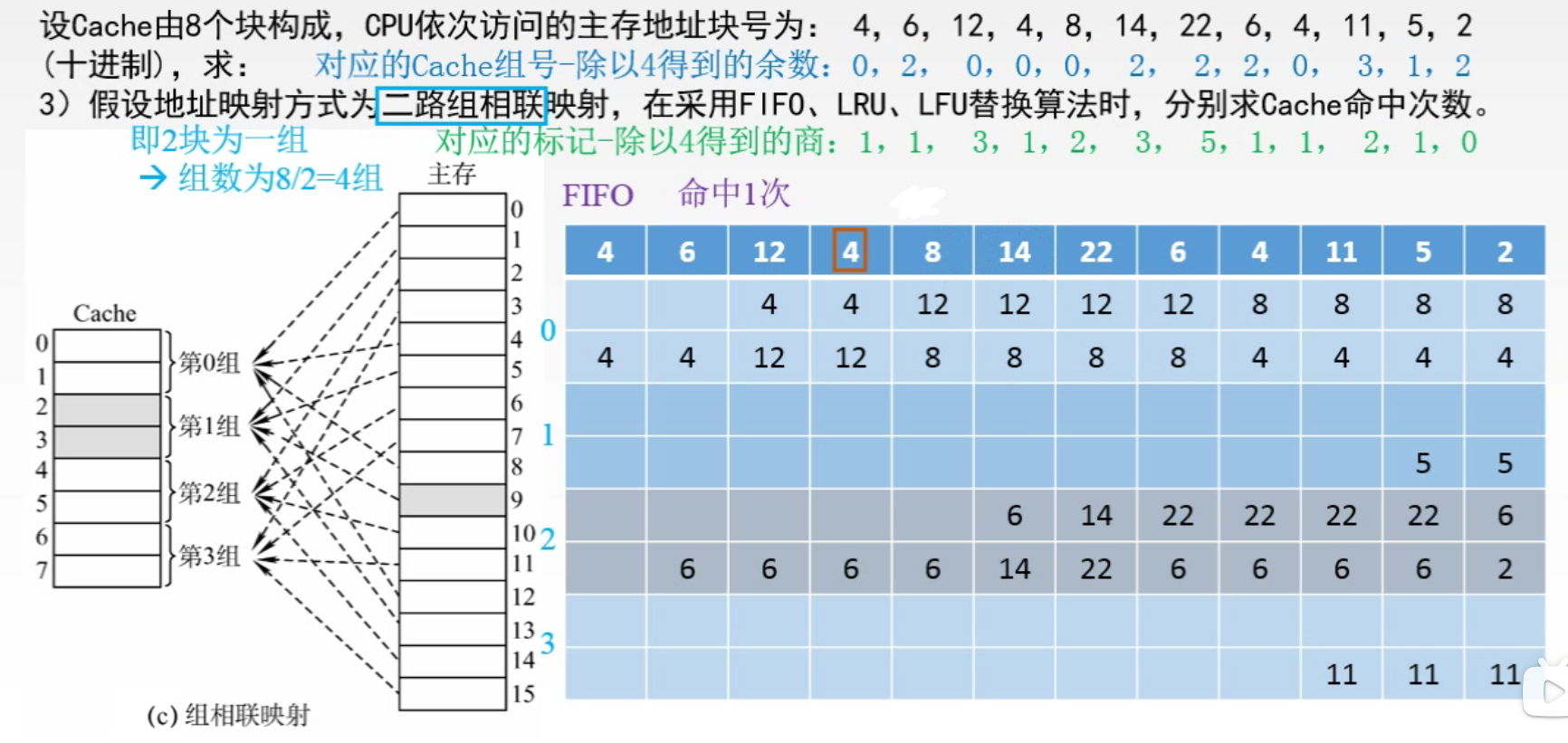

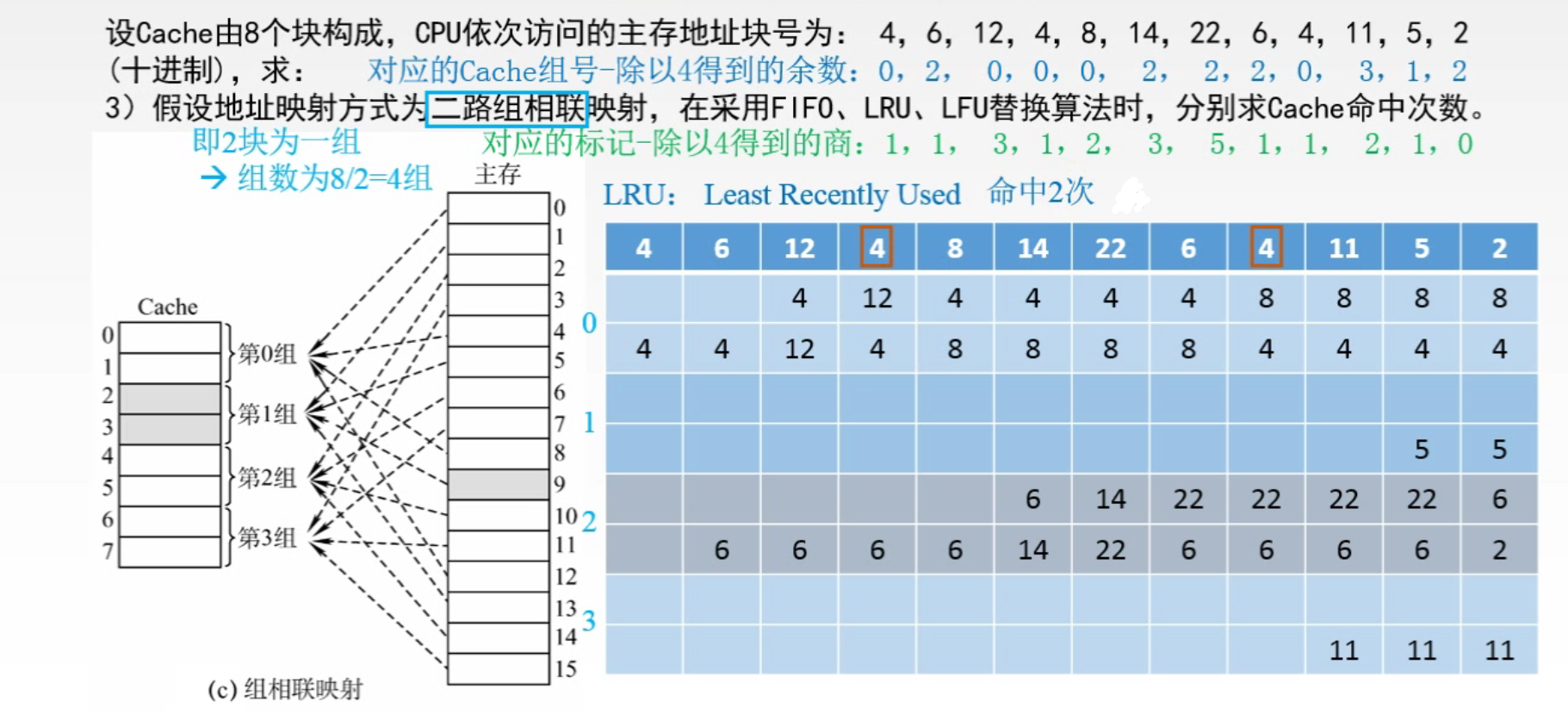

組相聯映射

某一主存塊 j 按模 Q 映射到 緩存 的第 i 組中的任一塊

🔔 n 路組相聯:Cache n 個塊為一組,即 Q = n

1️⃣ 當 n = 1 時,Cache 分成 1 組,相當於全相聯映射

2️⃣ 當 n = Cache 塊行數時,Cache 的每個塊都是一組。相當於直接映射

三種映射方式的總結

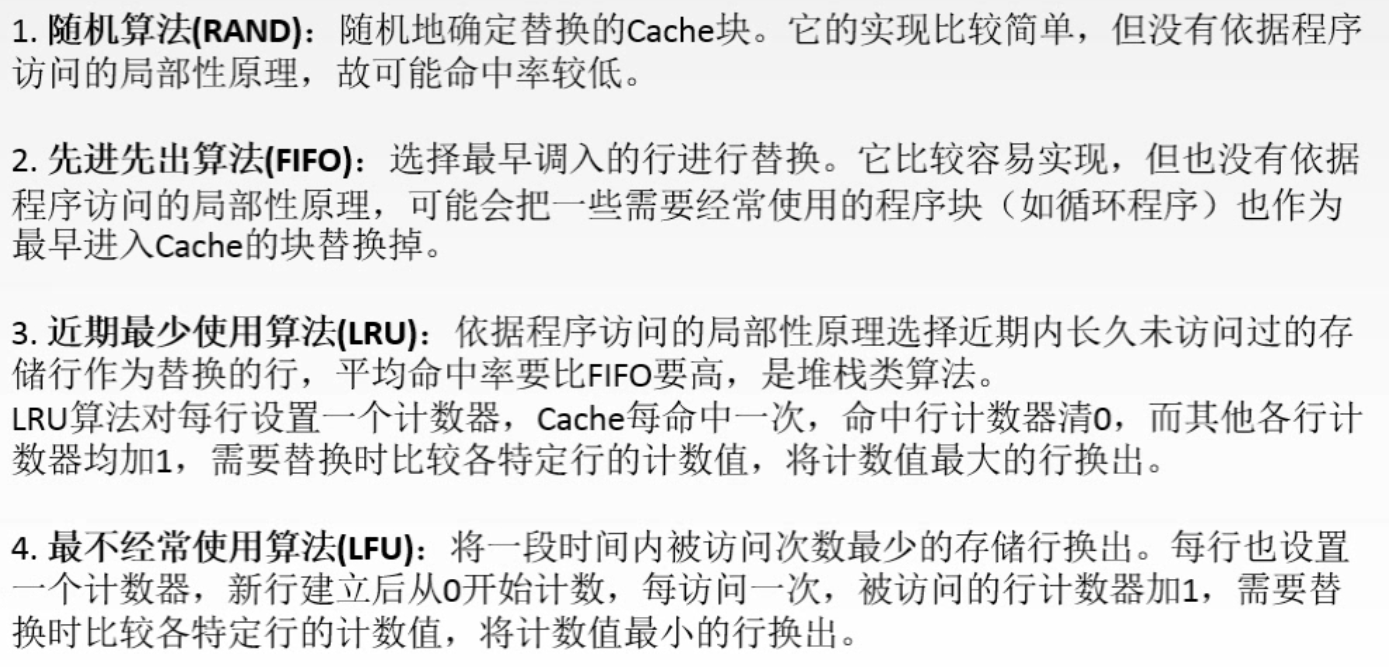

替換算法

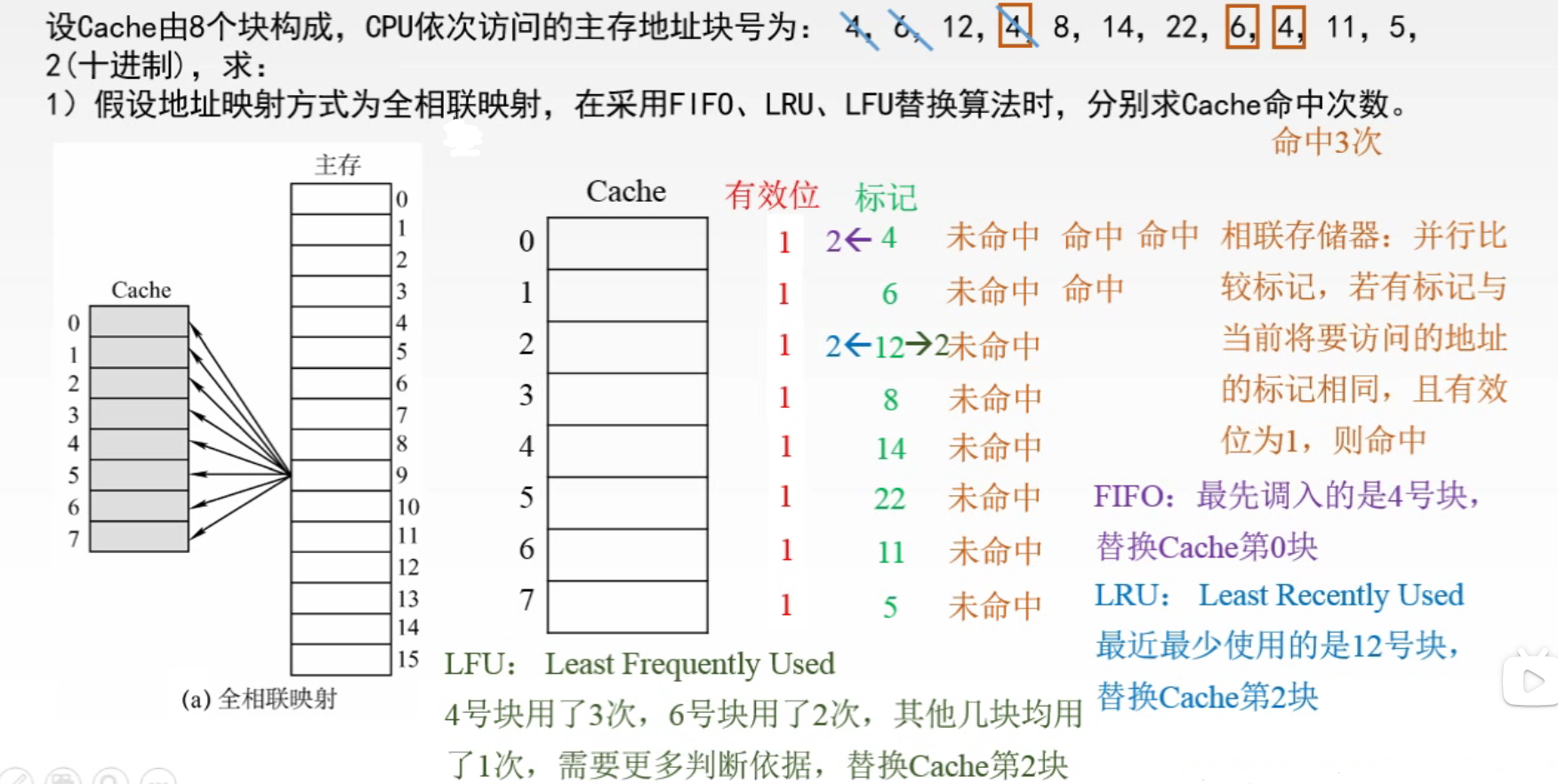

例題一

🌈 FIFO:每個組內,就是一個小的隊列,組內整體向上移動一個單位,新元素放下面,彈出最上面的元素

🌈 LRU:每個組中,最不常用的放最上,剛剛用到的(命中)的放最下;遇到新的元素且組滿,則組內整體向上移動一個單位,新元素放最下,彈出最上面的元素

例題二