FPGA 開發詳細流程你了解嗎?

- 2019 年 10 月 3 日

- 筆記

FPGA 的詳細開發流程就是利用 EDA 開發工具對 FPGA 芯片進行開發的過程。

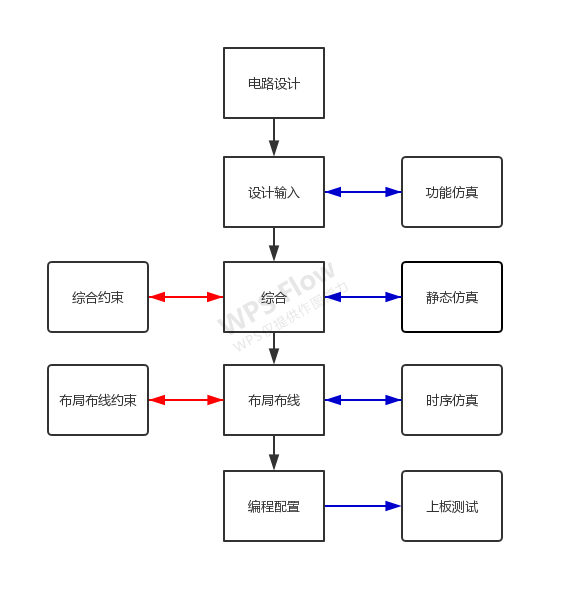

FPGA 的詳細開發流程如下所示,主要包括電路設計、設計輸入、綜合(優化)、布局布線(實現與優化)、編程配置五大步驟,其中,還有功能仿真、靜態仿真、時序仿真三大仿真,以及綜合約束、布局布線約束(包括位置約束和時序約束)兩大約束等等。

1、電路設計(FPGA Design)

在電路設計之前,首先要進行的是算法的設計與驗證(在 Python 或 Matalb 中完成)(至於算法是怎麼來的,一般是根據市場需求來開發的,這個就不在本次討論之中了)、方案論證、架構設計和 FPGA 芯片選型等準備工作。系統工程師根據任務要求,如系統的指標和複雜度、成本、功能性和穩定性、性能、對工作速度(延時和工作頻率)和芯片本身的各種資源、功耗等等方面進行權衡(藍色加粗部分也是數字電子系統的五大設計目標),選擇合理的設計方案(浮點定點、設計優化)和合適的 FPGA 器件類型(如 Cylone、Spartan、Artix、Virtex、Kintex、還是 Zynq 或者是 Zynq UltraScale + 等等)。

電路設計方法分為自底向上和自頂向下的設計方法。一般都採用自頂向下的設計方法(從系統設計開始,逐漸向模塊設計、器件設計和版圖設計等更物理的層次推進):從系統設計開始入手,然後把整體系統分成若干個基本單元,然後再把每個基本單元劃分為下一層次的基本單元,一直這樣做下去,直到可以直接使用 EDA 元件庫為止。最後,才開始 Coding。

2、設計輸入(Design Entry)

設計輸入指的是將設計者所涉及的電路以開發軟件要求的某種形式表達出來,並輸入到相應的軟件中的過程。最常見的設計輸入的表達方式為 IP 核、原理圖(Schematic)和 HDL 文本輸入。

這裡的 IP 按照來源的不同可以分為三類,第一種是來自前一個設計的內部創建模塊(Design by Yourself),第二種是 FPGA 廠家,第三種就是來自 IP 廠商。而按照產品交付的形式,IP 核又分為軟核(HDL 形式描述的功能塊)、硬核(版圖形式:提供設計的最終階段產品,即掩膜)、固核(網表形式:完成了綜合的功能塊)。

FPGA 廠家和 IP 廠商可以在 FPGA 開發的不同時期提供給我們不同的 IP。我們暫且知道他們分別是未加密的 RTL 級 IP、加密的 RTL 級 IP、未經布局布線的網表級 IP、布局布線後的網表級 IP。

3、綜合(Synthesis)

綜合一般指的是將高級抽象層次的設計描述自動轉化為較低層次描述的過程。而在 FPGA 中的綜合則是指自動實現如下轉換的軟件工具,或者說,綜合器就是能夠將原理圖或者 HDL 文本語言、描述的電路編譯成由與或陣列、RAM、觸發器、寄存器等邏輯單元組成的電路結構網表的工具。

綜合包括編譯、映射和優化(也可以分開不被綜合所包含),編譯就是 HDL → 門級網表,映射就是門級網表 → LUT,優化就是優化設計( 需要說明的是在 Altera 的開發流程中,將編譯、映射過程按照我們敘述的合稱為綜合,而在 Xilinx 的開發流程中,由設計輸入得到門級網表的過程叫做綜合,而映射過程歸結到其叫做實現的某一子步驟中。不過這都是小問題,整體的流程還是遵循這個順序的)。

綜合的形式:

1、將算法、行為描述轉換到 RTL 級(Register Transfer Level)(寄存器傳輸級),即從行為描述到結構描述。

2、將 RTL 級描述轉換到邏輯門級(包括觸發器),稱為邏輯綜合。

3、將邏輯門表示轉換到版圖表示,或者 PLD 器件的配置網表表示;根據版圖信息能夠進行 ASIC 生產,有了配置網表可完成基於 PLD 器件的系統實現。

這邊介紹一下數字系統設計器件:

數字系統器件的實現從以前的 PLA(可編程邏輯陣列)、PAL(可編程陣列邏輯)、GAL(通用陣列邏輯)發展到如今的 PLD(可編程邏輯器件 Programmable Logic Device)(包括現場可編程門陣列 FPGA(Field Programmable Gate Array)和複雜可編程邏輯器件 CPLD(Complex Programmable Logic Device))(半定製)、ASIC(專用集成電路 Application Specific Integrated Circuits)(全定製)。

軟件程序編譯器是將 C 或彙編語言等編寫的程序編譯為 0,1 代碼流,而硬件綜合器是將 Verilog HDL 等語言編寫的程序轉化為具體的電路網表結構。

在電路設計中,網表(Netlist)是用於描述電路元件相互之間連接關係的,一般來說是一個遵循某種比較簡單的標記語法的文本文件。(百度百科 門級網表)。綜合就是邏輯綜合器根據約束條件把 Verilog HDL 或 VHDL 描述的 RTL 級設計,轉換為可與 FPGA/CPLD 的門陣列基本結構相映射的網表文件。

4、布局布線(Place & Route)

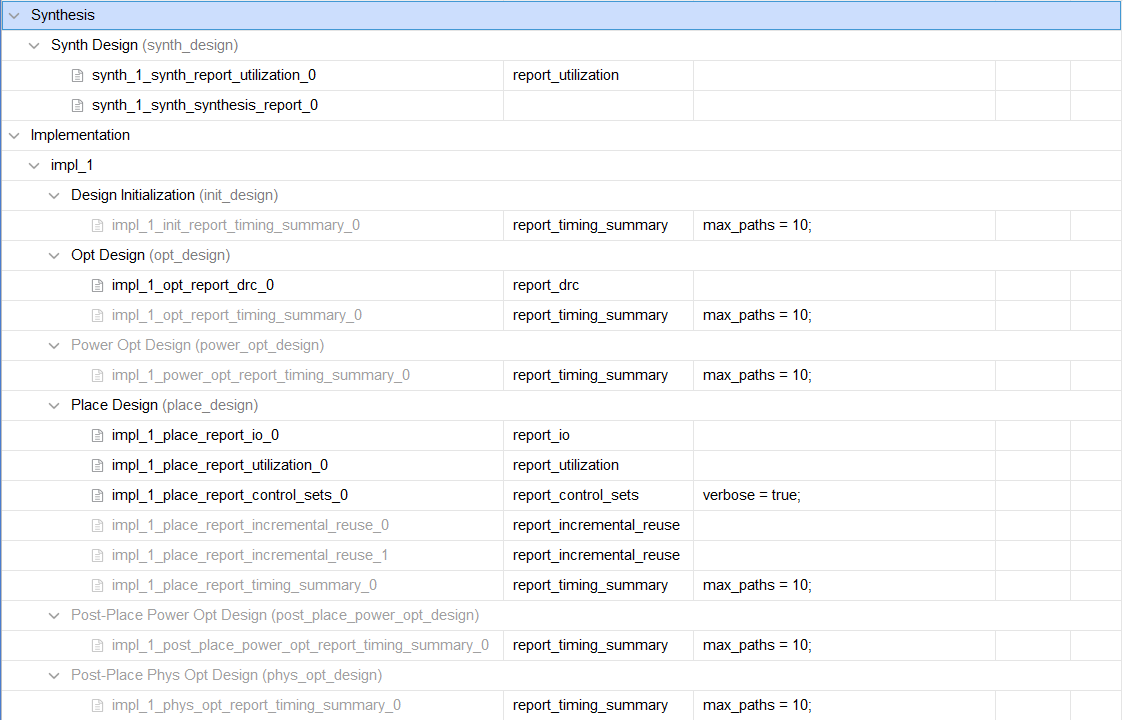

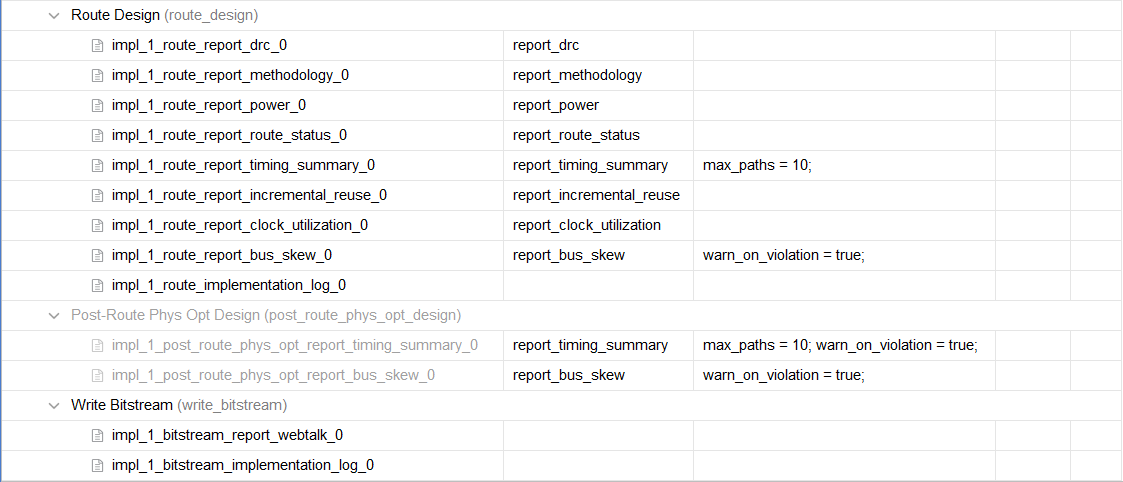

談及布局布線之前,首先要談到實現(Implementation)。實現就是將綜合生成的邏輯網表配置到具體的 FPGA 芯片上,而布局布線就是其中最重要的過程。Vivado 中的實現具體如下所示,分為設計初始化(Design Initialization)、優化設計(Opt Design)、功耗優化設計(Power Opt Design)、布局設計(Place Design)、後布局功耗優化設計(Post-Place Power Opt Design)、後布局物理優化設計(Post-Place Phys Opt Design)、布線設計(Route Design)、後布線物理優化設計(Post-Route Phys Opt Design)、生成比特流(Write Bitstream)。

布局布線指的是將綜合生成的電路邏輯網表映射到具體的目標器件中實現,併產生最終的可下載文件的過程。

布局是將已分割的邏輯小塊放到器件內部邏輯資源的具體位置,並使它們易於連線;

布線則是利用器件的布線資源完成各功能模塊之間和反饋信號之間的連接。

布局布線完成之後將產生如下一些重要的文件:

1、芯片資源耗用情況報告。

2、面向其他 EDA 工具的輸出文件,如 EDIF 文件等。

3、產生延時網表結構,以便於進行精確的時序仿真,這時候的仿真結果能夠比較精確地預測未來芯片的實際性能。如果仿真結果達不到設計要求,就需要修改源代碼或者選擇不同速度的器件,直至滿足設計要求,例如普通加法器改為超前進位加法器,普通乘法器改為 Booth 乘法器等等,通過減少關鍵路徑來滿足時序要求。

4、器件編程文件:如用於 FPGA 配置的 SOF,JAM,BIT 等格式的文件,用於 CPLD 編程的 JEDEC,POF 等格式的文件。由於布局布線與芯片的物理結構直接相關,所以一般選擇芯片製造商提供的開發工具進行此項工作。

約束(Constraint)(附加):

約束分為綜合約束和布局布線約束,布局布線約束又可以分為位置約束、時序約束。約束,就是對這些操作環節定製規則,定製條件,比如引腳約束和時序約束。一般開發環境會對這些約束有個默認,這些默認的設置對大部分情況下還是適用的,但是通常布局布線約束中的 I/O 約束是我們每一個工程都必須給定的。

仿真(Simulation)(附加):

仿真指的是對所設計電路功能的驗證。仿真包括(功能)RTL 仿真、(門級)靜態仿真和時序仿真。

RTL 仿真就是對你的 HDL 代碼仿真,對你的 RTL 級描述的設計進行測試。RTL 仿真,又叫功能仿真,也稱為前仿真,是在編譯之前對用戶所設計的電路進行邏輯功能驗證,此時的仿真沒有任何延遲信息,是處於理想化狀態的,僅對初步的功能進行驗證。

靜態仿真指對綜合之後的 LUT 門級網表。靜態仿真,又叫門級仿真,也稱為綜合後仿真,在仿真時,把綜合生成的標準延時文件反標註到綜合仿真模型中去,可估計門延時帶來的影響,但不能估計線延時,此時的仿真也並不是十分準確,和布局布線後的實際情況還是有一定差距的。

時序仿真在選擇具體器件並完成布局布線後進行的包含延時的仿真。時序仿真,又叫布局布線後仿真,是指將布局布線的延時信息反標註到設計網表中來檢測有無時序違規的現象(即是否滿足時序約束條件或器件固有的時序規則,如建立時間、保持時間等等。而此時,不同器件的內部延時都不太一樣,不同的布局、布線方案所生成的延時也不太一樣)。時序仿真包含的延遲信息最全,也最精確,能較好地反映芯片的實際工作情況。

5、編程配置(Program & Configuration)

編程配置就是生成比特流之後將比特流載入 FPGA 芯片中的一個過程。

把布局布線後生成的編程文件裝入 PLD 器件中的過程稱為下載。

通常將對基於 EEPROM 工藝的非易失結構 CPLD 器件的下載稱為編程。一般芯片編程是指產生使用的數據文件(如比特流文件(.bit)),然後將編程數據下載到 FPGA 芯片中。

而將基於 SRAM 工藝結構的 FPGA 器件的下載稱為配置。

以上就是 FPGA 開發的詳細流程。大家如果有什麼問題可以在下面留言,一起學習與討論,也歡迎關注博主,博主會在接下來的時間經常發佈關於數字電路與 FPGA 的一些精品知識點。