利用system generator 生成vivado ip—以低通滤波器举例

前段时间自学了matlab和vivado联合推出的system generator工具,用来做数字信号处理,十分好用且使开发更便捷,下面举个例子来供大家一起学习下。

首先打开matlab命令行,输入simulink。注意要先安装system generator ,这个网上有教程。

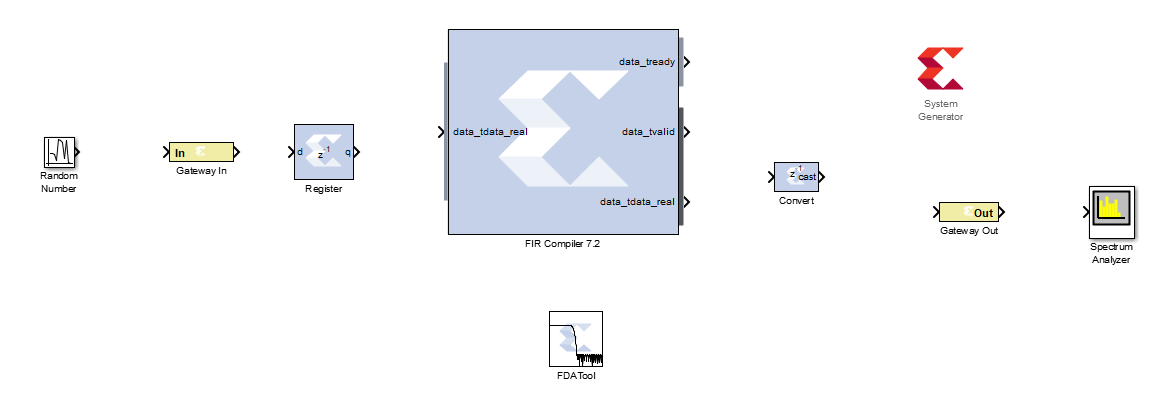

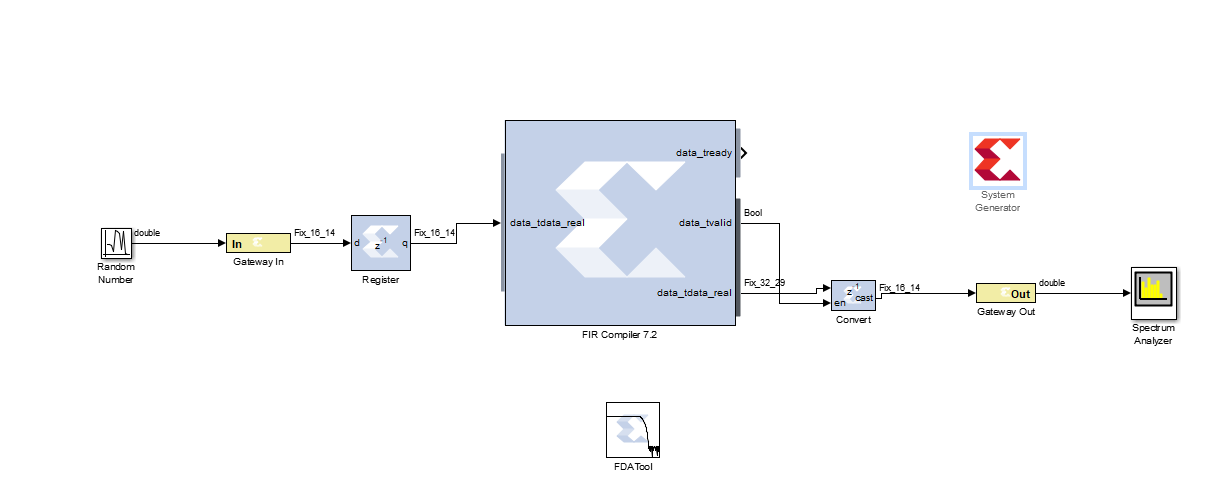

然后新建一个model,拖入模块成我这样:

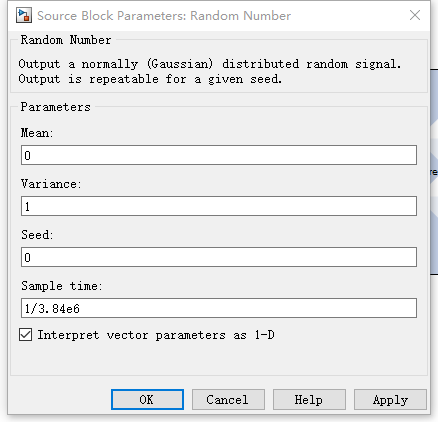

一个一个来设置:首先是信号源,采样率模逆的WCDMA码速率,为3.84Mcps。 然后是Gateway In,这个是IP核的输入端口,设定如下:

Register保持不变,事实上加不加好像都没什么影响。

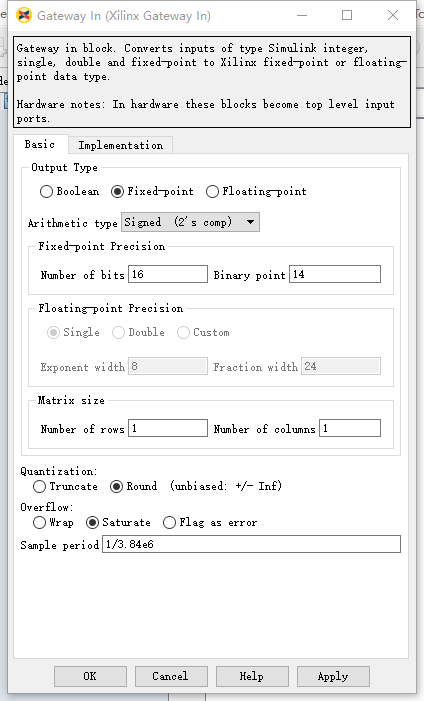

重点是滤波器的设计,先点开FDA tool,设计出一个通带截止点1MHz,阻带起始点1.2MHz的低通滤波器。

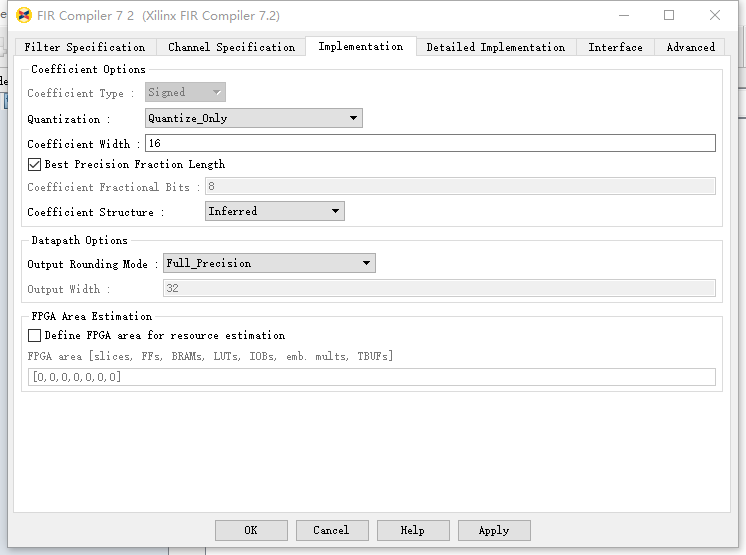

然后打开FIR compiler7.2,设置如下:1)输入xlfda_numerator(‘FDATool’),绑定一个FDATool;2)量化形式选成跟随FDATool量化,一般都是16bit保持不变。

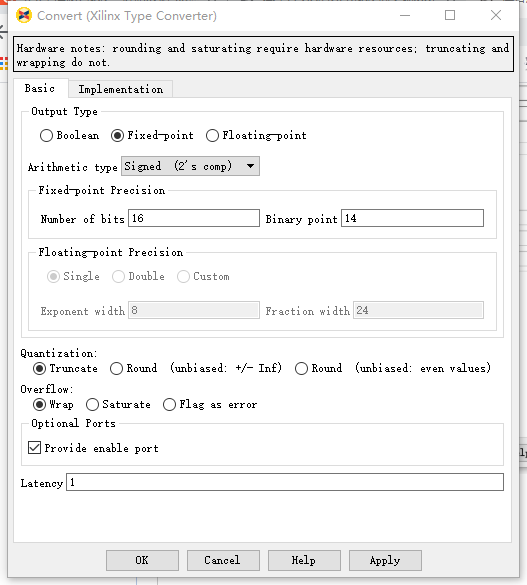

接着做截断处理,这一步关系着IP输出位宽。然后勾选Provide enanle port,这样就多了个截断使能信号。

默认16bit位宽,滤波器输出位宽32bit,截断为16bit,损失了一些精度,但是减小了输出位宽。如果你想看各模块的数据位宽,可以点击model的菜单栏的Display->signals&Ports->Ports Datas type。

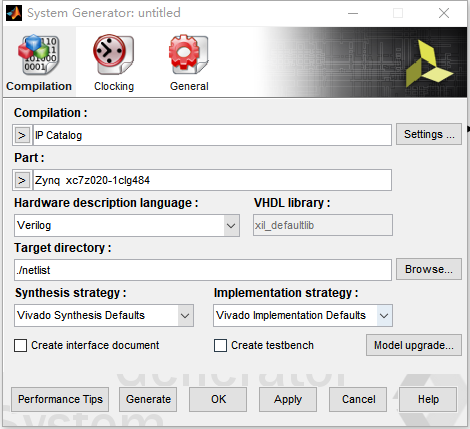

然后设置system generator:1)主要找到对应的FPGA芯片型号,只有对应的型号才能调用该IP。2)设计输入时钟,为该IP的主时钟,仿真时钟设置为3.84MHz。

最终连起来

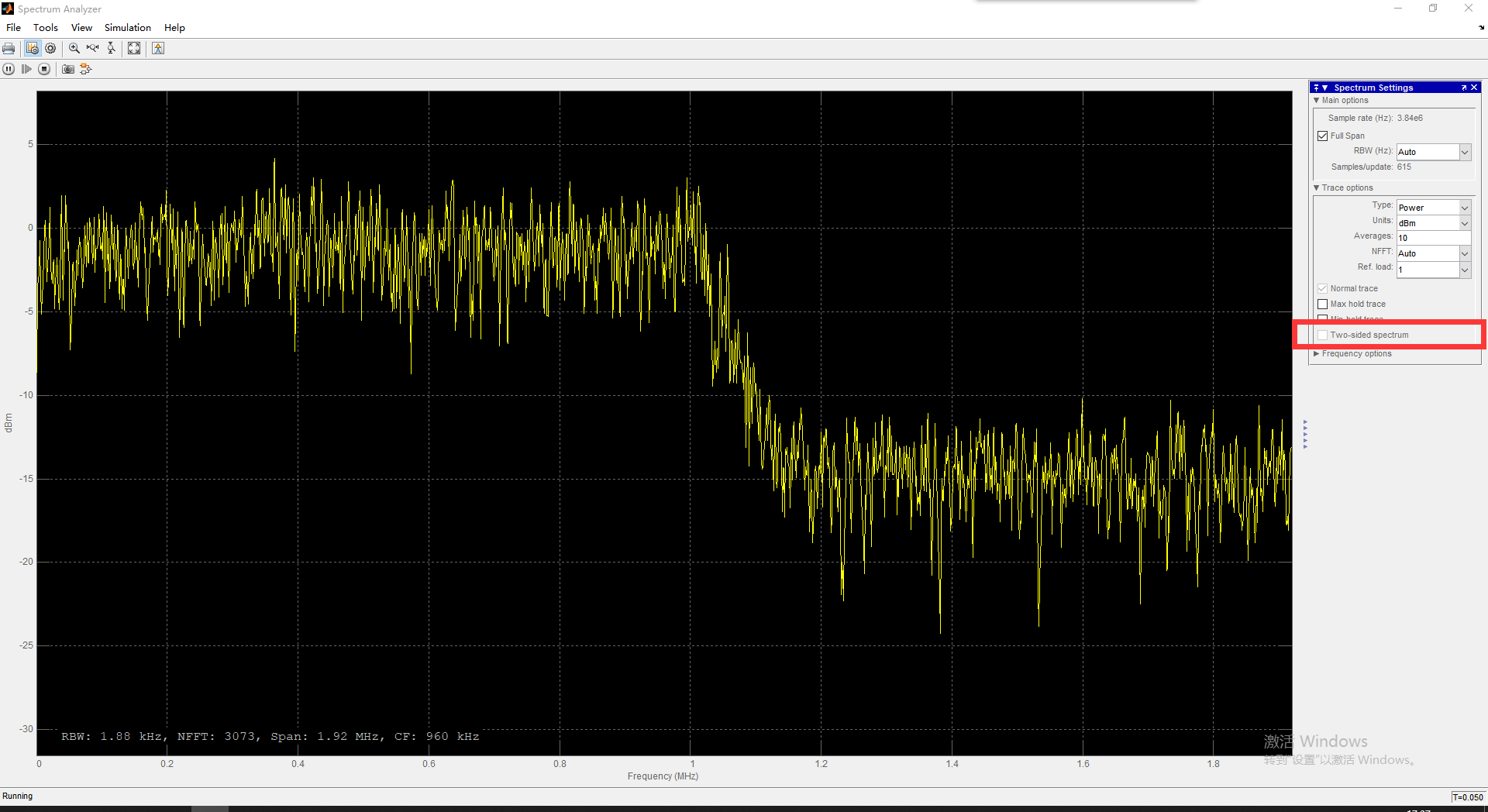

点击RUN,进行仿真,看看波形。频谱仪点红框可以看到双边谱,这里我就看了单边谱。

结论:因为我的信号源是3.84Mcps的脉冲信号,频谱无限大,被一个单级低通滤波器限制带1MHz,阻带1.2MHz,功率下降了15个dbm,但是滤波器设计的是衰减80个db,看来实际用起来还是有一定差距。

最后还是打开system generator,更改你想存放IP的文件夹,然后点gengerate。就生成了该低通滤波器的IP。

至于如何在vivado中导入IP,网上也是有很多教程,这里就不细说了。