JK觸發器與模12計數器

JK觸發器

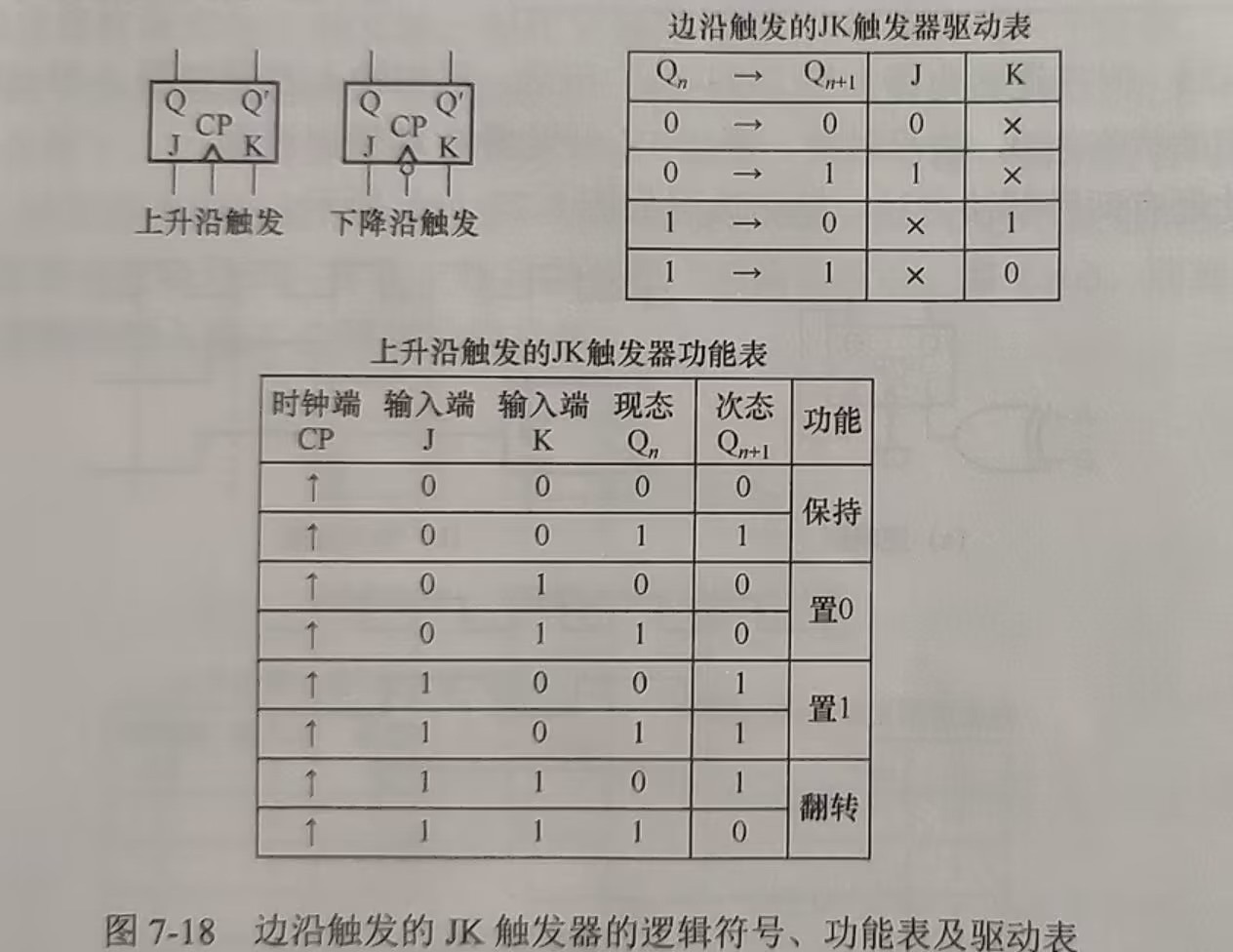

JK觸發器具有保持,置0,置1和翻轉四個功能。

則可得出次態方程:\(Q_{n+1} = JQ_n’+K’Q_n\)

Design

`timescale 1ns / 1ps

module jk(clk,Reset,Set,J,K,Q);

input clk;

input Reset;

input Set;

input J;

input K;

output Q;

reg q;

always@(posedge clk)

if(!Reset)

begin

q <= 1'b0;

end

else if(!Set)

begin

q <= 1'b1;

end

else

begin

case({J,K})

2'b00 : q <= q;

2'b01 : q <= 0;

2'b10 : q <= 1;

default : q <= ~q;

endcase

end

assign Q=q;

endmodule

Simulation

`timescale 1ns / 1ps

module JK_sim();

reg Reset, Set, clk;

wire Q;

reg J, K;

jk uu(clk, Reset, Set, J, K, Q);

initial

begin

Reset = 0;

Set = 0;

clk = 1;

J = 0;

K = 0;

#40 Reset = 1;

#40 Set = 1;

end

always #20{J, K} = {J, K} + 1;

always #10 clk = ~clk;

endmodule

波形圖

模12計數器

需要使用4個JK觸發器,卡諾圖化簡後得到觸發器控制函數的最簡與或式如下:

\(J_1 = K_1 = 1\)

\(J_2 = K_2 = Y_1^{n}\)

\(J_3 = (Y_4^n)’Y_2^nY_1^n\)

\(K_3 = Y_2^nY_1^n\)

\(J_4 = Y_3^nY_2^nY_1^n\)

\(K_4=Y_2^nY_1^n\)

Design

`timescale 1ns / 1ps

module count(Reset,Set,clk,Y);

input Reset;

input Set;

input clk;

output [3:0]Y;

wire j1,j2,j3,j4,k1,k2,k3,k4;

assign j1 = 1;

assign k1 = 1;

assign j2 = Y[0];

assign k2 = Y[0];

assign j3 = (~Y[3])&Y[1]&Y[0];

assign k3 = Y[0]&Y[1];

assign j4 = Y[0]&Y[1]&Y[2];

assign k4 = Y[0]&Y[1];

jk_0 u1 (clk,Reset,Set,j1,k1,Y[0]);

jk_0 u2 (clk,Reset,Set,j2,k2,Y[1]);

jk_0 u3 (clk,Reset,Set,j3,k3,Y[2]);

jk_0 u4 (clk,Reset,Set,j4,k4,Y[3]);

endmodule

Simulation

`timescale 1ns / 1ps

module sim_dev1();

reg Reset,Set,clk;

wire [3:0]Y;

initial

begin

Reset = 0;

Set = 0;

clk = 1;

#20 Reset = 1;

#20 Set = 1;

end

always#20 clk = ~clk;

CNT12 u(Reset,Set,clk,Y);

endmodule

波形圖

vivado使用JK觸發器IP核來實現計數器

-

新建JK觸發器項目。

-

新建Design Sources。

-

將前面JK觸發器的程式碼粘貼進去。

-

點擊Tools,點擊Create and package new IP。

-

Next,選擇Package your current project,Next,複製一下IP核的位置。

-

退出當前項目,新建計數器項目。

-

點擊Settings,再點開IP,點擊Repository。

-

點擊加號,粘貼剛剛複製的路徑。

-

然後點擊Select,OK。

-

現在點擊PROJECT MANAGER 中的IP Catalog。

-

看到我們剛剛添加的IP核了。

- 雙擊這個IP核,彈窗點擊OK,再OK,點擊Generate生成。

- 現在實現計數器,粘貼我們剛剛的程式碼。記得JK觸發器的名字要改為和剛剛生成的IP核的名字一樣(一般默認是 {name}_0 )。

- 完成,可以試試模型模擬。