JTAG 標準IEEE STD 1149.1-2013學習筆記(一·)Test logic architecture、Instruction register以及Test data registers

我是 雪天魚,一名FPGA愛好者,研究方向是FPGA架構探索和SOC設計。

關注公眾號【積體電路設計教程】,拉你進「IC設計交流群」。

註:轉載請註明出處

一、Test logic architecture

首先此測試邏輯架構必須包含的組件有

- 一個 TAP 控制器

- 一個指令暫存器 IR

- 一組測試數據暫存器 DR

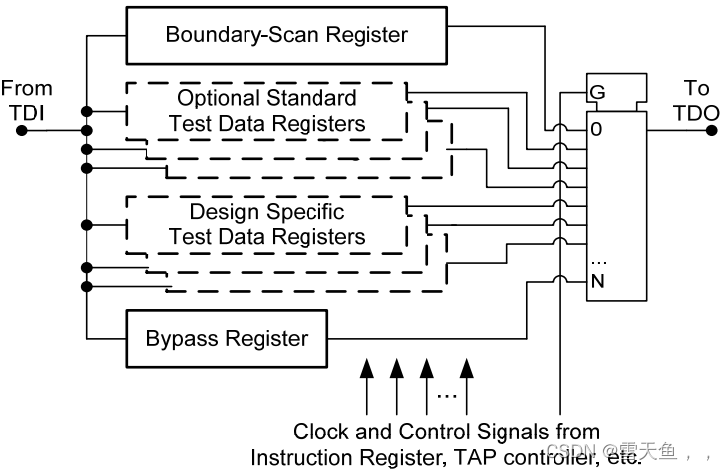

測試邏輯架構示意圖如圖1所示

下面簡單介紹下此示意圖:

(1)TAP 控制器接收TCK,TMS和TRST(可選)訊號,產生 IR、DR和其他組件所需的時鐘和控制訊號,控制所要執行的操作,如複位、移位、捕獲和更新等。

(2)IR 指令解碼選擇所要進行操作的DR

(3)TMP控制器是可選組件,可接收指令解碼訊號,用於修改TAP控制器產生的一些控制訊號。

所以此測試邏輯,就是通過JTAG介面根據指令去對DR進行讀操作或者寫操作,寫數據從TDI輸入,讀數據從TDO輸出。

二、Instruction register

參考JTAG標準第七章指令暫存器(Instruction register)

顧名思義,指令暫存器用來存儲指令的,指令通過TDI輸入到指令暫存器,再通過指令解碼,產生對應控制訊號, 用於選擇要執行的測試操作或要訪問的測試數據暫存器(DR)。

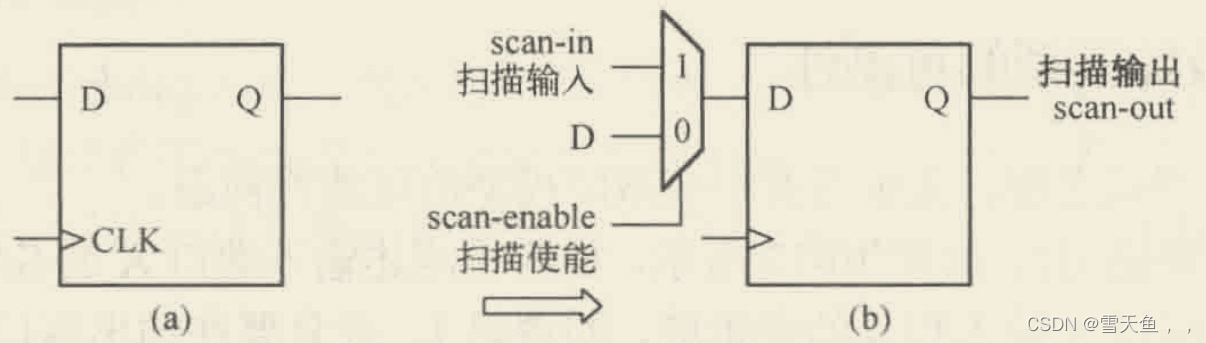

2.1 D型掃描觸發器

在正式介紹IR結構之前,先介紹下帶多路選擇器的D型掃描觸發器,此掃描觸發器是掃描測試結構的基本單元。

掃描觸發器有兩種工作模式,分別為:

- 正常工作模式:scan_enable 為 0,此時數據從D端輸入,從Q端輸出。

- 掃描移位模式:scan_enable 為 1,此時數據從scan_in 輸入,從scan_out輸出(Q與scan_out復用)

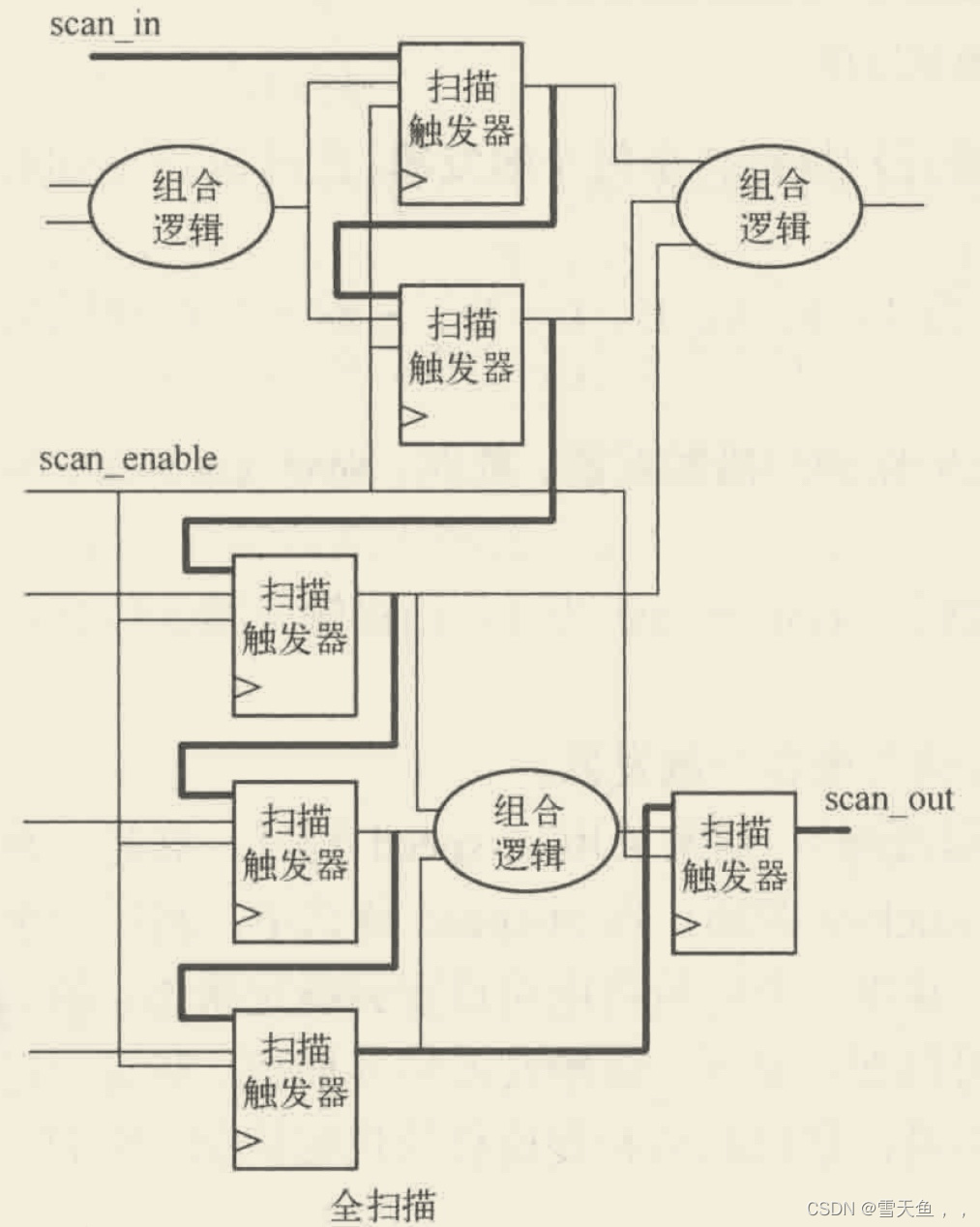

將這種掃描單元按照掃描移位模式連接起來,就構成了掃描測試中的基本結構,這裡僅簡單介紹全掃描。全掃描就是多個掃描單元相連接,上一單元的掃描輸出,連接到目前單元的掃描輸入,目前單元的掃描輸出連接到下一單元的掃描輸入,以此類推,構成一條移位暫存器鏈,如圖2所示:

這樣的掃描結構,可通過一個串列輸入端,將期望的數據存入移位暫存器鏈並觀察運行結果。

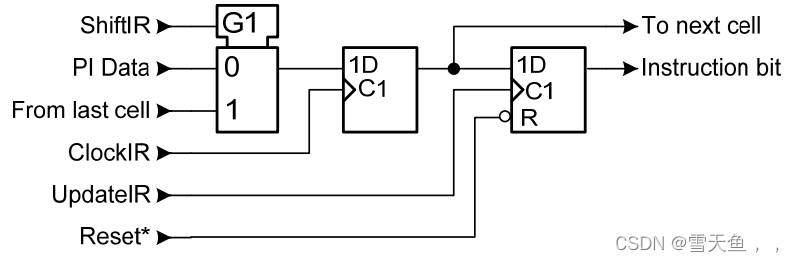

2.2 IR 電路結構

指令暫存器的電路結構與全掃描類似,同樣是採用了移位暫存器鏈。其掃描單元如圖3所示:

| 訊號名 | 作用 |

|---|---|

| ShiftIR | 移位使能 |

| PI Data | 並行輸入數據 |

| From last cell | 掃描輸入(數據來自上一掃描單元的掃描輸出埠) |

| ClockIR | 掃描單元時鐘訊號,僅在Capture-IR和Shift-IR狀態時有效 |

| Update IR | 指令位觸發器時鐘訊號,僅在Update-IR狀態時有效 |

| Reset | 複位訊號,用於強制性指令解碼(BYPASS或IDCODE) |

| To next cell | 掃描輸出(連接到下一掃描單元的掃描輸入埠) |

| Instruction bit | 指令位,指示是否為該指令位對應的指令 |

構成的移位暫存器鏈如圖4所示:

掃描路徑已經用紅色筆標註了,所以IR就是根據TAP輸出的控制訊號,來進行對應的移位,更新,捕獲等操作,解碼器對指令進行解碼,並將對應的指令位置1並輸出來控制測試邏輯架構其他組件。其中在 Test-Logic-Reset 狀態時,Instruction1將被複位,表示強制性指令BYPASS或者IDCODE。

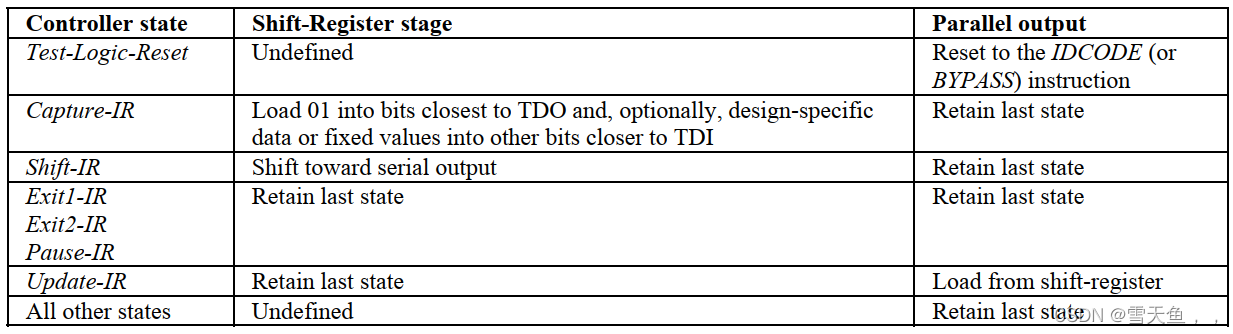

2.3 指令暫存器的操作

在不同的 TAP 控制器狀態下,IR進行的操作不同,詳情見圖5:

可以看到 IR 掃描單元存儲值只在Shift-IR狀態和Capture-IR狀態發生改變,且指令只在 Test-Logic-Reset 和 Update-IR 狀態更新並生效,其中前者是複位到強制性指令BYPASS或者IDCODE,後者則是更新為解碼器結果。

三、Test data registers

參考JTAG標準第九章測試數據暫存器(Test data registers)、第10章旁路暫存器(Bypass register)、第11章邊界掃描暫存器(boundary-scan register)。

此標準所定義的測試邏輯架構中,測試數據暫存器至少要包括兩種暫存器,分別為旁路暫存器(Bypass Register)和邊界掃描暫存器(boundary-scan register),當然也有其他可選暫存器,如設備ID暫存器、晶片ID暫存器、初始化數據暫存器等。

3.1 TDR的實現

TDR是由多個測試數據暫存器組成,每個數據暫存器又基於移位暫存器實現,從而可以通過串列輸入將數據寫入選中的數據暫存器中,一種實現方案如圖1所示:

實線繪製的暫存器為必須實現的數據暫存器,虛線繪製的暫存器為可選實現的。可以看到數據通過TDI埠串列輸入到DR中,再通過MUX選擇要輸出的數據,經TDO埠輸出。

下面簡單介紹下所實現的一些DR。

3.2 Bypass Register

該暫存器只有一個移位暫存器,即只能存儲1bit數據,存在的意義是當進行某項測試操作時,不需要訪問其他的DR,那麼TDI就選擇從旁路暫存器通過,從而減少對感興趣段的測試訪問時間,也就是讓數據能儘快從TDI達到感興趣段。

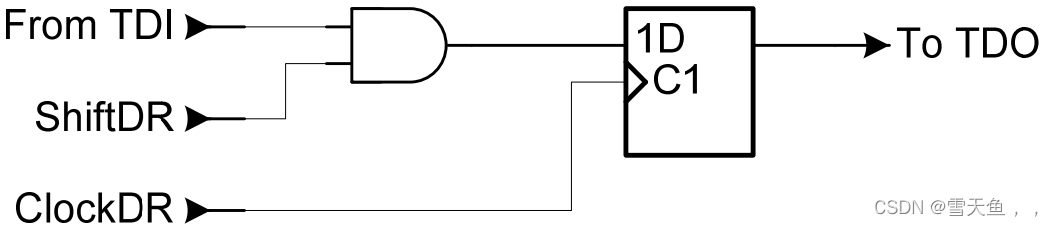

實現的電路結構圖如圖2所示:

| 訊號名 | 作用 |

|---|---|

| ShiftDR | 移位使能 |

| From TDI | 串列掃描輸入 |

| ClockDR | 移位時鐘訊號,僅在Capture-DR和Shift-DR狀態時有效 |

標準中提供了一個例子:

現有一個包含 100 個晶片的電路板,每個晶片的邊界掃描暫存器中有 100 位。 如果所有晶片同時串聯連接,則電路板上的邊界掃描路徑將包括 10000 個移位暫存器。 現在需要僅訪問測試路徑上的一個晶片,這會導致測試時間過長。但若存在旁路暫存器的話,便可大大減少路徑上經過的移位暫存器級數,具體方法是將 99 個晶片設置為僅通過其旁路暫存器進行移位,而被測晶片在路徑中仍是通過邊界掃描暫存器去測試。 這將使總串列路徑級數減少為 199 級,與 10000 級相比大幅減少。

3.3 Boundary-scan register

在DR中,邊界掃描暫存器(BSR)是最複雜了,標準中用來解釋該暫存器的篇幅也比較長,這裡簡單介紹一下,後續等自己理解加深後再更新。

該組件有輸入輸出管腳,輸入輸出緩衝器,輸入訊號分為時鐘訊號和非時鐘訊號,輸出訊號部分可通過一些控制訊號控制其輸出。

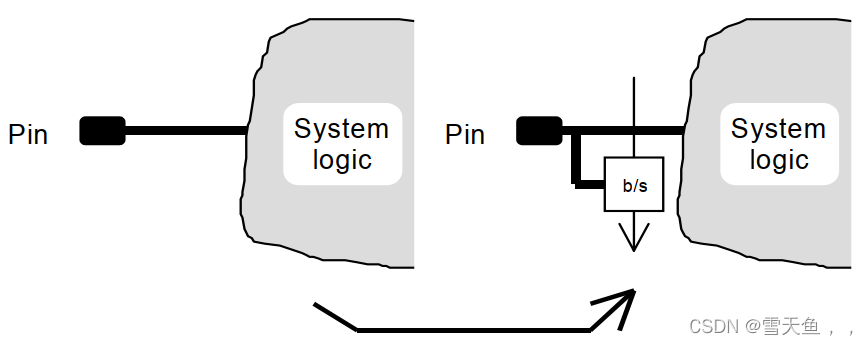

BSR的作用就是用來觀察這樣一個片上系統邏輯的輸入輸出引腳傳輸的數據,接下來介紹一下BSR單元

- 「observe-only」單元

為三端單元,兩個輸入端,一個輸出端,其中一個輸入端接Pin,用於將輸入或者輸出管腳的訊號載入到移位暫存器中,另外兩個埠用於與其他單元相連接,組成完整的掃描鏈。

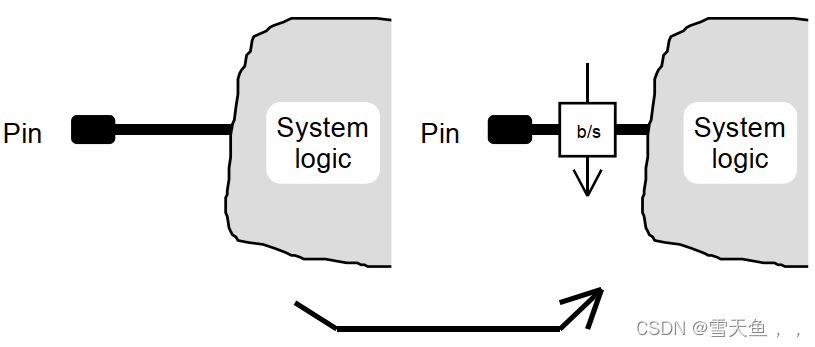

- 「control-and-observe」 單元

為四端單元,兩個輸入埠,兩個輸出埠,其中一個輸入端接Pin,用於將輸入或者輸出管腳的訊號載入到移位暫存器中,一個輸出埠用於將存儲的數據載入到Pin上,另外兩個埠用於與其他單元相連接,組成完整的掃描鏈。此單元構成的BSR就可以將期望的測試輸入向量載入到晶片中。

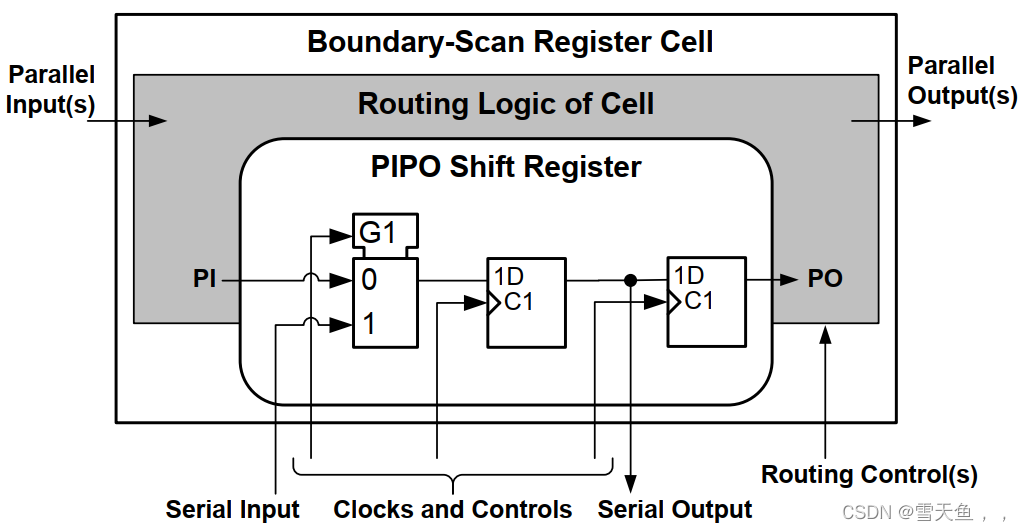

其內部結構如圖6所示:

這裡多了一些輸入埠,傳輸時鐘訊號和控制訊號,方便通過指令對BSR進行一些操作。

參考文獻

【1】IEEE Standard for Test Access Port and Boundary-Scan Architecture IEEE Std 1149.1™-2013

【2】SoC設計方法與實現 第三版 郭煒

- 更多技術文章和學習資料,請關注我的公眾號:【積體電路設計教程】

- 全平台統一:【雪天魚】