計組

- 2021 年 6 月 28 日

- 筆記

- reading notes

概論

高級語言 又稱演算法語言,面向解決實際問題所用的演算法,瞄準處理問題和解題過程的程式

彙編語言 是對電腦機器語言進行符號化處理的結果,再增加一些方便程式設計而實現的擴展功能

在彙編語言中,可以用英文或縮寫替代二進位的指令程式碼,更容易記憶和理解

機器語言 是電腦硬體能直接識別和運行的指令的集合,是二進位碼組成的指令

程式最小的執行單元是指令。

翻譯程式 將高級語言翻譯成機器語言程式的軟體

- 編譯程式 將用戶編寫的高級語言程式的全部語句一次全部翻譯成機器語言程式

- 解釋程式 將源程式的一條語句翻譯成對應於機器語言的一條語句,並且立即執行

電腦體系結構 是指那些能夠別程式設計師所見到的電腦系統屬性,即概念性的結構和功能特性

電腦組成 是指如何實現電腦體系結構所體現的屬性,它包含了許多對程式設計師來說透明的硬體細節

馮·諾依曼電腦

- 電腦由運算器、存儲器、控制器、輸出和輸入五設備五大部件組成

- 指令和數據以同等地位存放在存儲器內,並可以按地址尋訪

- 指令和數據均用二進位數表示

- 指令有操作碼和地址碼組成,操作碼用來表示操作的屬性,地址碼用來表示操作數在存儲器中的位置 (在操作數這個欄位中可以放操作數本身,也可以放操作地址,還可以放操作地址的計算方法)

- 指令在存儲器內按順序存放,通常指令是順序執行的,在特定的條件下,可以根據運算結果或設定的條件改變執行順序

- 機器以運算器為中心,輸入輸出設備與存儲器間的數據傳送通過運算器完成(所以有了匯流排)

CUP Central Processing Unit

ALU Arithmetic Logic Unit 算術邏輯單元,用來完成算術邏輯運算

- ACC Accumulator 累加器

- MQ Multiplier_Quotient Register 乘商暫存器

- X 操作數暫存器

CU Control Unit 控制單元 用來解釋存儲器中的指令,並發出各種操作命令來執行指令

- PC Program Counter 用來存放當前欲執行的指令地址,和MAR有通路

- IR Instruction Register 用來存放當前指令,從MDR中讀取到的指令

- CU Control Unit 用來分析當前指令所需完成的操作,並發出各種微操作命令序列,用以控制所有被控制的對象

一條指令執行包括三個過程:取址、分析、執行

- 取址:命令暫存器讀出一條指令

- 分析:對指令分析,指出該完成什麼操作,並按照定址特徵指明操作數的地址

- 執行:根據操作數所在的地址以及指令的操作碼完成某種操作

MM Main Memory

- MAR Memory Address Register 存儲器地址暫存器:用來存放訪問單元的地址,位數代表存儲單元的個數。

- MDR Memory Data Register 存儲器數據暫存器:用來存放從存取體某單元取出的程式碼或者準備往某存儲體存入的程式碼

現在的CPU中集成了MAR和MDR

機器字長 指CPU一次能夠處理數據的位數,通常與暫存器的位數有關

存儲容量 = 存儲單元個數(MAR) × 存儲字長(MDR)

運算速度 用單位時間內執行命令的平均條數來衡量,並用MIPS(Million Instruction Per Second)作為計量單位

CPI Cycle Per Instruction 執行一條指令所需要的的時鐘周期(機器主頻的導數)

FLOPS Float Point Operation Per Second 每秒浮點運算次數

匯流排

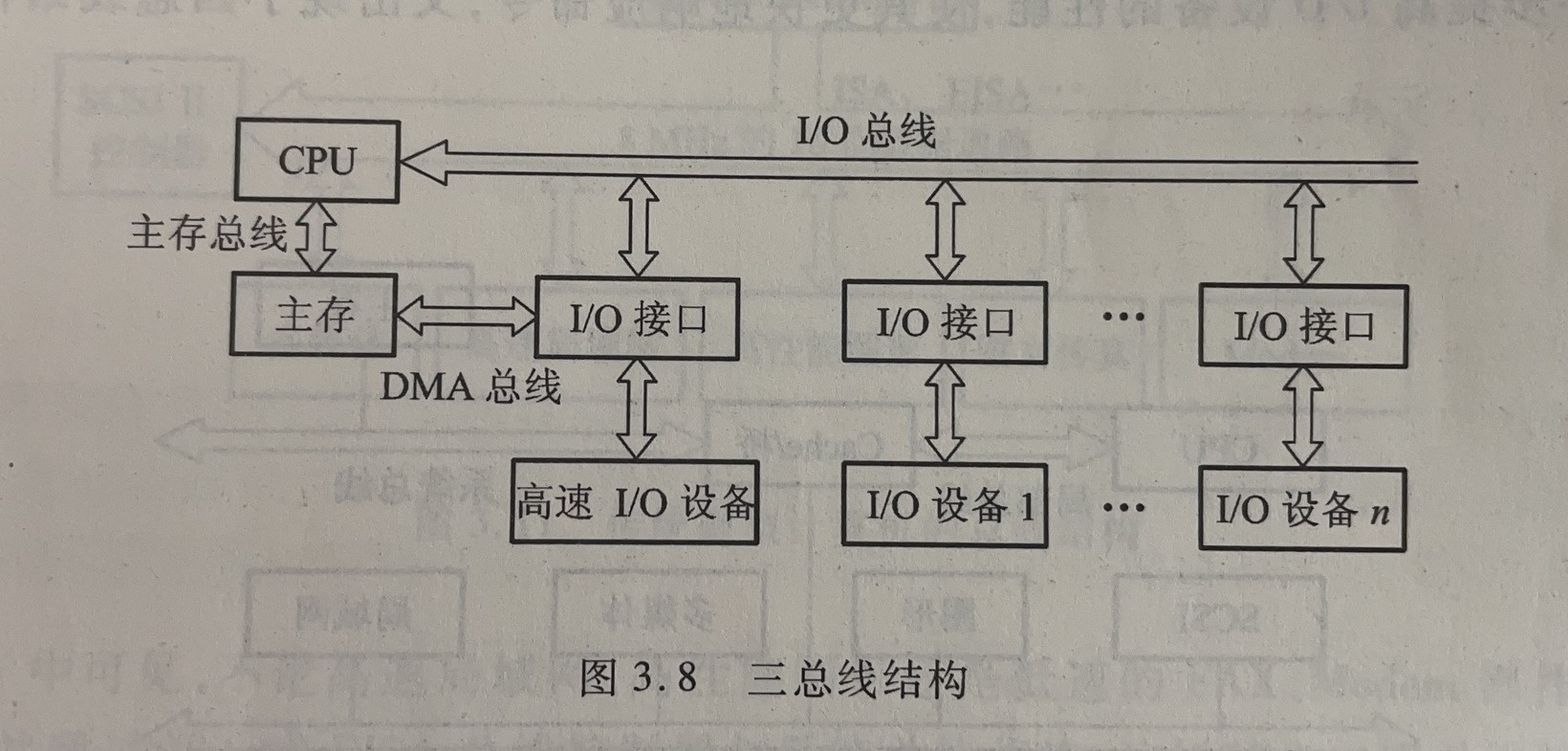

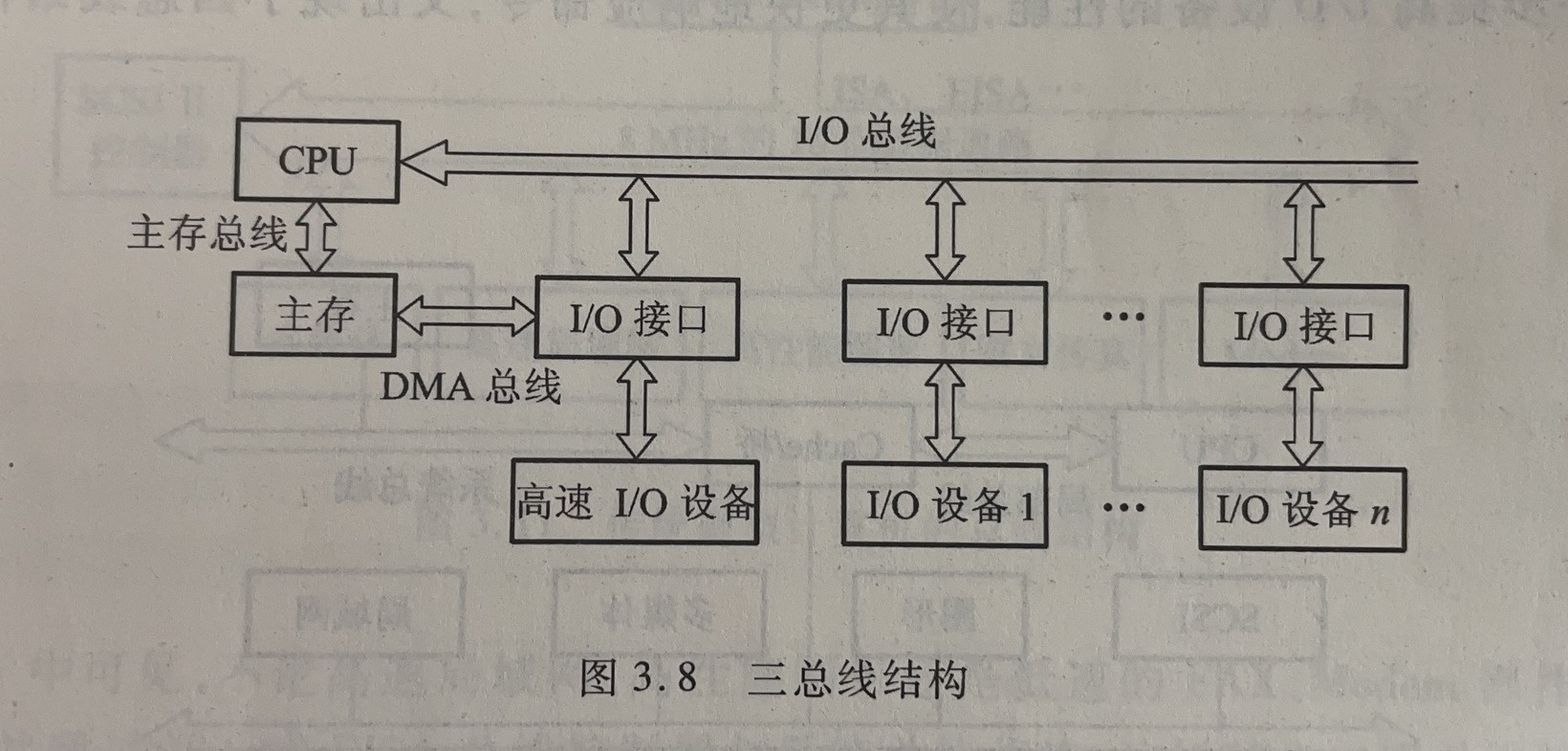

單匯流排多匯流排之間的變化:

- 單匯流排到雙匯流排 將速度較低的I/O設備從從單匯流排上分離出來

- 雙匯流排到三匯流排 將I/O匯流排中高速設備連接到DMA匯流排上

- 三匯流排到四匯流排 將主存匯流排 分為 局部匯流排(CPU 和 Cache)和系統匯流排(MM 和 Cache)

匯流排通訊控制

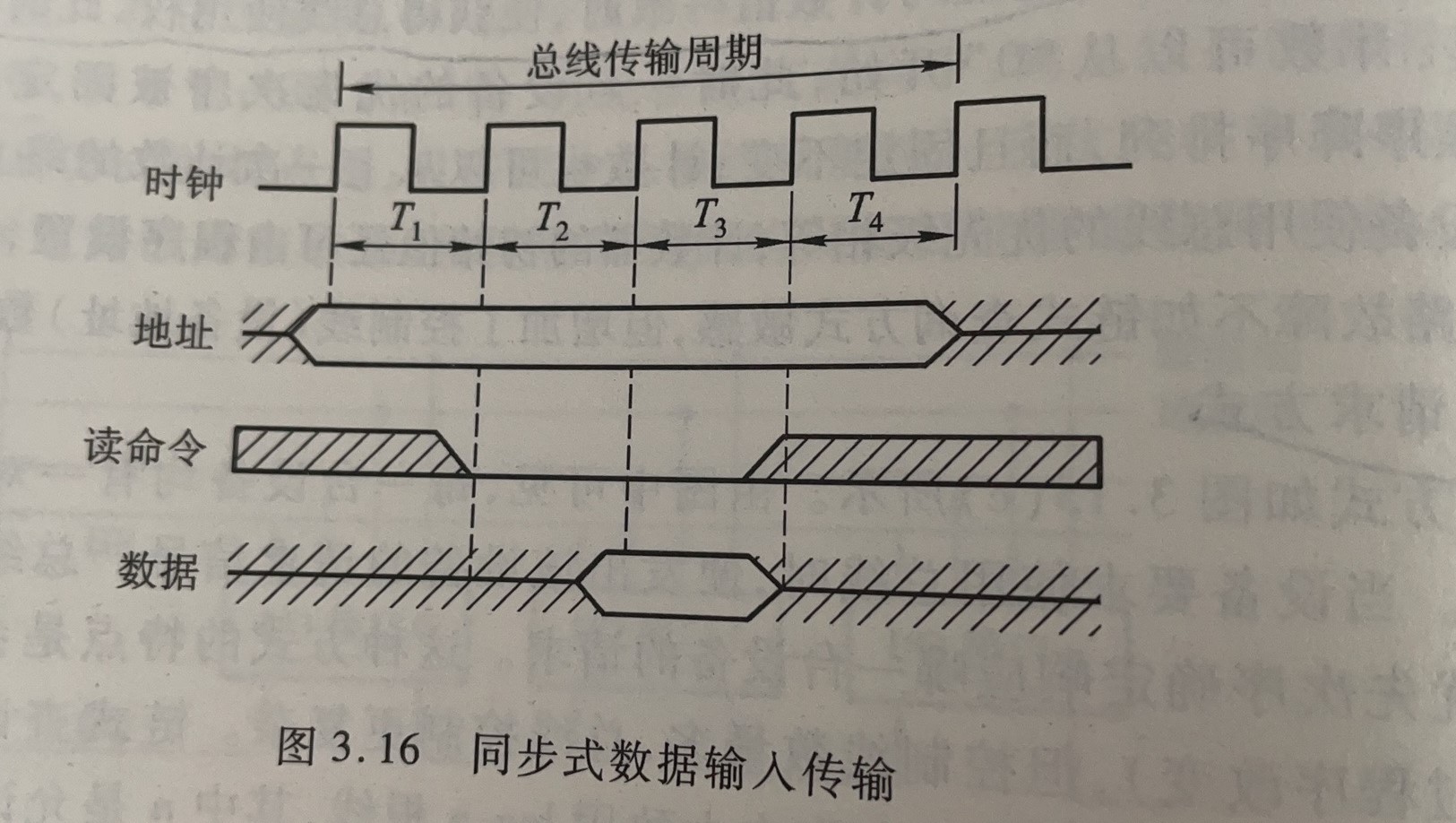

同步通訊

CPU在T1上升沿發出地址資訊;在T2上升沿發出讀命令;在T3上沿到來之前,將CPU所需要的數據送到數據匯流排上;在T3始終周期里內將數據線上的資訊送到內部暫存器中;在T4的上沿撤銷讀命令,撤銷對數據匯流排的驅動。

適用於匯流排長度較短,各部件的存取周期一致的場合

非同步通訊

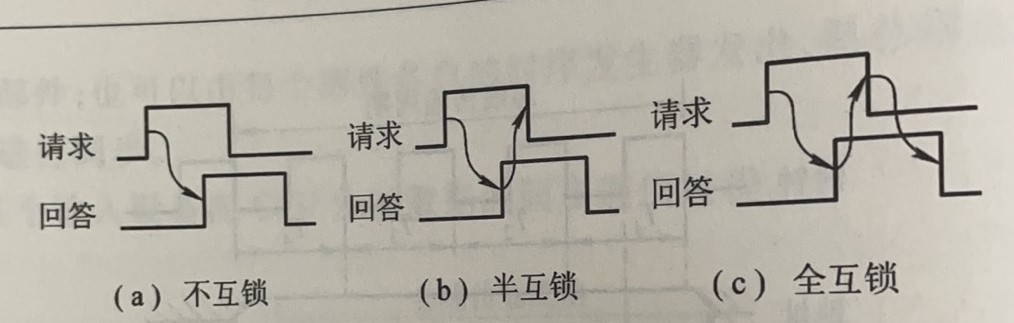

非同步通訊分為不互鎖,半互鎖,全互鎖三種

不互鎖:主模組發出請求訊號後,不必等待從模組的回答訊號,而是經過一段時間後,確認從模組已經收到請求訊號後,便撤銷其請求訊號。

半互鎖:主模組發出請求訊號,必須待接到從模組的回答訊號後再撤銷其請求訊號,有互鎖關係;而從模組在接到請求訊號發出的回答訊號,但不必等待獲知主模組的請求訊號已經撤銷,而是隔一段時間自動撤銷回答訊號,無互鎖關係。

全互鎖:主模組發出請求訊號,必須待從模組回答後在撤銷其請求訊號;從模組發出回答訊號,必須待獲知主模組請求訊號已撤銷後,在撤銷其回答訊號。

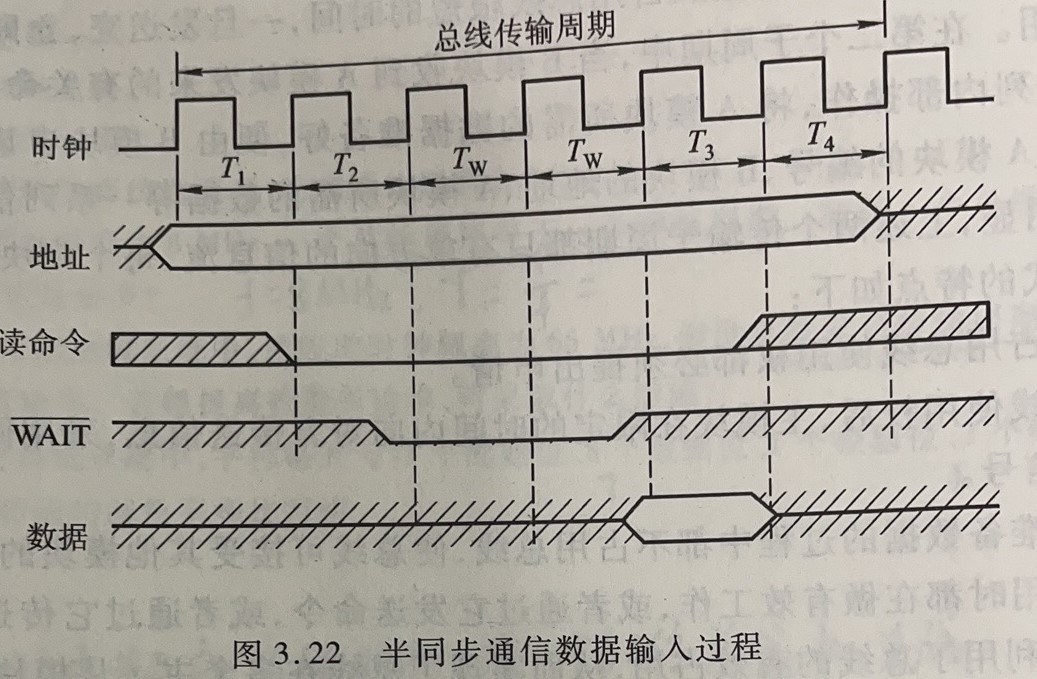

若從模組工作速度慢,在T3時鐘周期無法提供數據,則必須在T3到來前通知主模組,給出低電平訊號;若主模組在T3周期到來之前檢測到了低電平訊號,則插入一個時鐘周期Tw

分離式通訊省略

存儲器

RAM(Random Access Memory) 隨機存儲,存儲的時間和存儲單位的物理位置無關

- 靜態的 SRAM(以觸發器原理存儲資訊)和 動態的 DRAM(以電容充放電原理存儲資訊 需要每2ms使用刷新放大器刷新 防止資訊丟失)

ROM(Read Only Memory) 只能讀,不能寫入

- MROM 由廠家製作不可再次寫入 行列選擇線交叉處可以由MOS管 也可以沒有

- PROM 由雙極電路和熔絲構成 可一次寫入不可修改

- EPROM 使用浮動柵MOS電路,給漏端加高電壓,浮動柵浮起阻斷電路;紫外線照射擦除

- EEPROM 電可擦存儲器,Flash Memory

輔存

- 磁碟 光碟 磁帶

快取

- cache

串列存儲器 對其讀寫時,需要按其物理位置的先後順序尋找地址

存儲容量 = 存儲單元個數 x 存儲字長 (能存儲二進位碼的總位數)

存儲容量 = 存儲單元個數 x 存儲字長/8 (能存儲位元組的總位數)

存儲速度

- 儲周期(連續兩次獨立的存儲操作時間所需的最小間隔時間 MOS 100ns TTL 10ns)

- 存取時間(讀或者寫時間)

存儲器頻寬 單位時間記憶體儲的資訊量 (T 500ns 16位 頻寬為 32M位/秒)

存儲器與CPU連接

存儲容量的擴展

- 位擴展:增加存儲字長

- 字擴展:增加存儲器的數量

- 字位同時擴展

地址線的連接:通常將CPU地址線的低位與存儲芯的低位相連。CPU的高位用於存儲芯擴充,片選線等

數據線的連接:必須對存儲晶片擴位,使其數據位數與CPU相等

讀寫命令線的連接:CPU的讀寫命令線一般直接和存儲晶片的讀寫端相連,通常高電平位讀,低電平位寫。

片選線的連接:存儲器由許多存儲晶片組成,哪一片被選中完全取決於該存儲晶片的片選控制端是否接收到來自CPU的片選有效訊號;且片選有效訊號和訪存控制訊號有關(若訪問I/O,則訪存控制訊號位高電平,表示不要求存儲器工作);CPU中沒有與存儲晶片連接的高位地址線必須和訪存控制訊號共同產生存儲晶片的片選訊號。

存儲器的校驗

二進位位數為n,需要校驗k位,組成n+k位程式碼滿足:2^k >= n + k +1

漢明碼偶校驗:只需⊕ 1, 3, 5, 7 2, 3, 6, 7 4, 5, 6, 7得到 C1, C2, C3

提高訪存速度

單體多字系統:適用於指令和數據在主存內時連續存放的

多體並行系統:採用多體模組組成的存儲器。每個模組都有相同的容量和存儲速度,各模組都有獨立的MAR、MDR、地址解碼器、驅動電路和讀寫電路,他們既能並行工作又能交叉工作。

多體模組由存控器來控制。它由排隊器、控制線路、節拍發生器、及標記觸發器等組成。

I/O系統

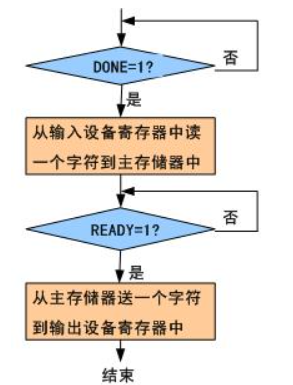

①程式查詢方式:表示從鍵盤輸入一個字元到處理機,再把這個字元輸出到顯示器上的工作過程。當DONE標誌為”1″,表示已經從鍵盤輸入一個字元到設備緩衝暫存器,在這個字元被CPU取走後,DONE標誌複位。輸出設備的標誌READY的設置與輸入設備正好相反,當READY標誌為”1″時,表示設備緩衝暫存器是空的,正準備接收從CPU送來的數據,在設備緩衝暫存器中已經有數據時,READY標誌複位,表示輸出設備正在把緩衝暫存器中的數據輸出到設備上。

②中斷輸入輸出方式:當輸入設備已經把數據準備就緒,或者輸出設備已經空閑時,要主動向CPU發出服務的請求。在CPU方面,每當執行完成一條指令後都要測試有沒有外圍設備的中斷服務請求,如果發現有外圍設備的中斷服務請求,則要暫時停止當前正在執行的程式,先去為外圍設備服務,等服務完成後再繼續執行原來的程式。

中斷輸入輸出方式的定義是:當出現來自系統外部,機器內部,甚至處理機本身的任何例外的,或者雖然是事先安排的,但出現在現行程式的什麼地方是事先不知道的事件時,CPU暫停執行現行程式,轉去處理這些事件,等處理完成後再返回來繼續執行原先的程式。

③直接存儲器訪問(DMA)方式

對於輸入設備:

- 從輸入介質上讀一個位元組或字到DMA控制器中的數據緩衝暫存器BD中,如果輸入設備是面向字元的,則要把讀入的字元裝配成字。

- 若一個字還沒有裝配滿,則返回到上面;若校驗出錯,則發中斷申請;若一個字已經裝配滿,則將BD中的數據送入主存數據暫存器。

- 把主存地址暫存器BA(在DMA控制器中)中的地址送入主存地址暫存器,並且將BA中的地址增值至下一個字地址。

- 把DMA控制器內的數據交換個數計數器BC中的內容減”1″。

- 若BC中的內容為”0″,則整個DMA過程全部結束,否則返回到最上面繼續進行。

對於輸出設備:

- 把主存地址暫存器BA(在DMA控制器中)中的地址送入主存地址暫存器,並啟動主存儲器,同時將BA中的地址增值至下一個字地址。

- 將主存儲器數據暫存器中的數據送入DMA控制器的數據緩衝暫存器BD中。如果輸出設備是面向字元的,則要把BD中的數據拆卸字元。

- 把BD中數據逐個字元(對於面向字元的設備)或整個字寫到輸出介質上。

- 把DMA控制器內的數據交換個數計數器BC中的內容減”1″。

- 若BC中的內容為”0″,則整個DMA過程全部結束,否則返回到最上面繼續進行。

④通道處理機

- 在用戶程式中使用訪管指令進入管理程式,由CPU通過管理程式組織一個通道程式,並啟動通道。

- 通道處理機執行CPU為它組織的通道程式,完成指定的數據輸入輸出工作。通道被啟動後,CPU就可以退出作業系統的管理程式,返回到用戶程式中繼續執行原來的程式,而通道開始與設備之間的數據傳送。當通道處理機執行完通道程式的最後一條通道指令”斷開通道指令”時,通道的數據傳輸工作就全部結束了。

- 通道程式結束後向CPU發中斷請求。CPU響應這個中斷請求後,第二次進入作業系統,調用管理程式對輸入輸出中斷請求進行處理。 如果是正常結束,管理程式進行必要的登記等工作,如果是故障、錯誤等異常情況,則進行例外情況處理。然後,CPU返回到用戶程式繼續執行。

- 位元組多路通道

如果連接在通道上的各個設備輪流佔用一個很短的時間片(通常小於100微秒)傳輸一個位元組,或者說,不同的設備在它所分得的時間片內與通道在邏輯上建立不同的傳輸連接,則稱為位元組交叉方式(Byte-interleave Mode)。如果允許一個設備一次佔用通道比較長得時間傳輸一組數據,或者說,設備與通道的連接可以根據需要維持到一組數據全部傳送完成,則稱為成組方式(Block Mode)

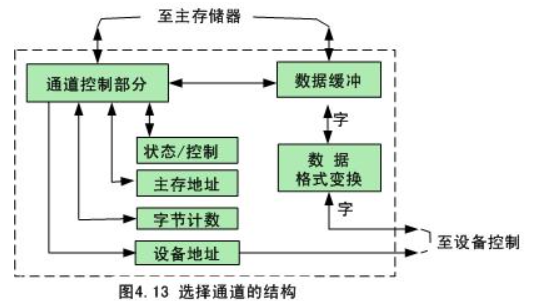

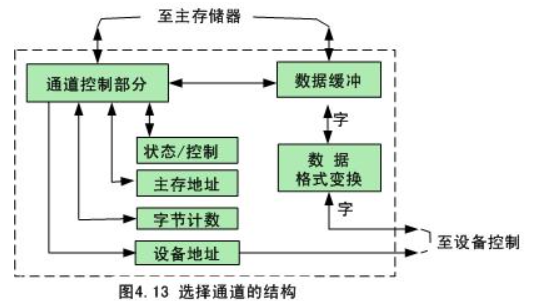

- 選擇通道

高速外圍設備必須設置專門的通道在一段時間內單獨為一台外圍設備服務,但在不同的時間內仍可以選擇不同的設備。一旦選中某一設備,通道就進入”忙”狀態,直到該設備的數據傳輸工作全部結束為止,這就是選擇通道(Selector Channel)

- 數組多路通道

從磁碟存儲器讀出一個文件的過程

第一步是定位,把讀寫磁頭移動到記錄該文件的磁軌上,這要依靠機械動作來完成,稱為定位時間,或找道時間,一般需要十毫秒左右。

第二步是找扇區,等待讀寫磁頭轉動到記錄該文件的起始扇區位置,稱為找扇區時間,或等待時間。等待時間的長短主要與兩個因素有關,一是磁碟的轉速,二是磁頭定位到所需要的磁軌時,磁頭所處位置與記錄該文件的起始扇區位置的相對距離。因此,等待時間的長短是隨機的,最長為磁碟轉一周所需的時間,最短為零。取平均值,通常稱為平均等待時間。目前,高速磁碟的轉速已經達到每分鐘5000轉以上,因此,磁碟存儲器的平均等待時間一般小於10毫秒。

第三步是讀出數據,目前,高速磁碟存儲器的數據傳輸率已經達到每秒33兆位元組以上。因此,讀出一個扇區(512個位元組)只需要十幾微秒時間。

數組多路通道在向一台高速設備發出定位命令後就立即從邏輯上與該設備斷開,直到定位完成時再進行連接,發出找扇區命令後再一次斷開,直到開始數據傳送。因此,數組多路通道的實際工作方式是:通道在為一台高速設備傳送數據時,有多台高速設備可以在定位或者在找扇區。

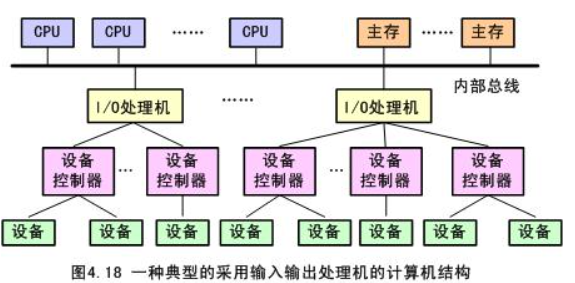

⑤輸入輸出處理機

輸入輸出處理機通常是一台獨立的處理機,具有一定的運算功能,可以承擔一般的外圍處理機的輸入輸出、控制操作和運算處理等任務。另外,由於輸入輸出處理機具有自己的存儲器,因此,不必通過主存儲器就能完成與外圍設備的數據交換。

[^1] 電腦組成原理 唐朔飛 第二版

[^2] 電腦體系結構 鄭緯民,湯志忠 第二版