基於4H-SIC的先進積體電路用n型LDMOS電晶體

- 2021 年 3 月 4 日

- 筆記

- 微電子&積體電路文獻翻譯

基於4H-SIC的先進積體電路用n型LDMOS電晶體

摘要:

通過對具有不同的設計方式的具有減小的表面電場的橫向4H-SIC-N型-橫向擴散金屬氧化物半導體(LDMOS)電晶體進行測量和模擬,得到了得出了不同的設計情況下積體電路中的電氣行為。在p型參雜的外延層中製作一個額外n型區域從而形成漂移區,這促進了減小表面電場並因此增強了擊穿能力。已有功率MOSFET的設計規則可與現有的20伏特4H-SIC的CMOS製程技術兼容。額外植入的減小表面電場區域在深度大約為390納米處為3.5×1012cm2。根據設計變化,測量到擊穿電壓在372至981伏範圍內時,導通電阻從1000下降至54兆歐姆·cm2。最佳測量品質因數(FOM,V2BD/RON)值為12.3MW/cm2。此外,提出的n-LDMOS電晶體的電氣行為與TCAD模擬模型進行了比較。據此,導出了有關溝道長度、漂移區和場板的設計準則,這將為進一步的研究提供依據。此外,根據模擬,1μm深的RESURF區域和6×1012cm-2的較高的RESURF注入劑量甚至會導致FOM值高於43 MW/cm2。

關鍵詞:4H-碳化硅(SiC)、積體電路(ICs)、橫向場效應電晶體、減小的表面電場(RESURF)。

一,引入

基於不同的p-和n-摻雜區域之間的電荷補償效應的橫向器件,如減小的表面電場(RESURF)結構,在硅中得到很好的驗證。RESURF結構的實現能夠使得在保證較高的擊穿電壓的同時獲得較低的傳導損耗。對於RESURF結構,在進行適當的器件設計時由於幾乎恆定不變的電場可以在器件表面提供一個橫向擊穿(低於標準的電場強度)。因此,擊穿將會以一個很大的值發生在垂直於p-n結的位置。橫向功率MOSFETs器件設計理念主要利用基於CMOS技術的積體電路。

由於器件電阻較高,高電壓CMOS技術的適用性被限制在120伏(600伏用於補償p/n結)。碳化硅(SiC,特別是4H-SiC多晶硅柵)中,RESURF結構器件還沒有很好地應用,儘管這些功率器件有新的可能性。在這裡,寬頻隙能夠獲得更高的理論電場強度,這使得更高的擊穿電壓成為可能。此外,由於可靠性因素,在強電場情況下減小SIC器件表面電場強度甚至比減小SI器件表面電場強度更加重要。然而,由於技術限制特別是在摻雜過程中的缺陷主要限制了電荷補償器件的實施。在本文中,研究了運用RESURF原理的n型-橫向-擴散-金屬-氧化物半導體電晶體(LDMOS)的電氣行為,包括測量和模擬之間的比較。該設計僅使用一個額外的掩模就能實現20V 4H-SiC CMOS技術(與其他地方介紹的10V 4H-SiC CMOS技術相比) 。這個CMOS的製作基於一個n型襯底上的p型外延層。對於積體電路,器件的電流路徑必須與襯底絕緣。例如,Yun等人提出了一種基於n型外延和n型襯底的品質非常好的橫向碳化硅金屬氧化物半導體場效應電晶體,但是當電流通過高摻雜襯底區域時,它並不適合積體電路應用。

二,4H-碳化硅RESURF器件的原理

RESURF結構的一般原理可以追溯到Apples和Vaes公司引入的橫向硅二極體結構。RESURF器件通過在現有的基礎上形成了一層額外的摻雜層,從而減少器件表面的電場強度進而受益。這個額外的層導致相鄰層形成電荷補償,因此導致空間電荷區延伸進入了截止區。RESURF區域的摻雜濃度和深度必須被調整到相鄰層的濃度。這種關係抑制了一個通過將電場的峰值轉移到垂直p-n結注入來實現的橫向器件發生雪崩擊穿時的表面附近擊穿。對於SIC,已經顯示出臨界電場在2至4MV/cm範圍內最理想的RESURF濃度為6×1012cm-2。

三,實驗

所提出的RERURF結構n-LDMOS電晶體的製造被集成到一種新的20V 4H-SIC CMOS技術中。1-微米三阱互補金屬氧化物半導體製程是弗勞恩霍夫集成系統和器件技術研究所(IISB)的特殊處理技術,用於硅以外的高壓和高溫應用,使用p摻雜外延區。用於高精度感測和放大的積體電路是一個新的成果。對於異常感測、集成放大、額外的UV p-i-n二極體、溫度感測器、電阻和電容等都可以在積體電路中實施。這裡介紹的LDMOS電晶體不是這些積體電路的一個完整部分,而是用包括高壓擴展模組在內的相同處理方式為未來的應用而簡化的。

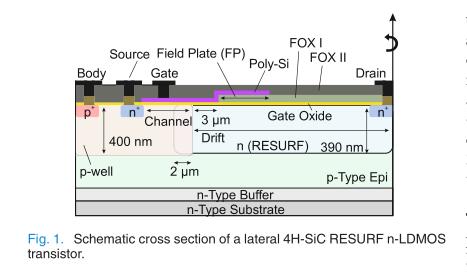

n-LDMOS已經被展示在了圖1中。在一個鋁摻雜的緩衝層(5μm厚,劑量5×1017cm-3)上生長一個輕摻雜鋁的外延層(9μm厚,劑量7×1014cm-3),防止垂直達到n型緩衝區(劑量1×1018cm-3,厚度1.2μm)和n型襯底。這種堆疊順序是由互補金屬氧化物半導體製程的設計規則給出的。為了使用工業標準,使用了n型SiC襯底。選擇兩個附加的p型層是為了避免CMOS電晶體的p阱區的離子注入。這個概念防止了在互補金屬氧化物半導體電晶體的溝道中的注入損傷。RESURF區域的剖面注入總劑量為3.5×1012 cm-3。我們使用的注入能量高達290千電子伏,導致最大注入深度約為390納米。由於所用光刻膠掩模的阻擋能力,注入能量被限制在這個值。為了保持製程流程的簡單,這種注入過程是一個沒有硬掩膜的過程,硬掩膜可以阻擋高強度的注入能量。器件的漂移區域從13 μm變化到80μm,溝道長度從1 μm變化到10μm,場板(FP)的橫向重疊在n-RESURF區域的3 μm到20μm處。電晶體的p摻雜溝道區大摻雜濃度大約為1×1017cm-3。由於光刻調整,RESURF區域與p阱重疊2μm。觸點是高度摻雜的p+和n+區域(~1019cm-3),深度分別約為400和270 nm。使用碳覆蓋層在氬氣氛中在1700℃下將注入的區域退火30分鐘。場氧化物的厚度為(402±5)納米。該氧化物通過TEOS製程沉積(乾燥,在900℃退火30分鐘)。柵極氧化物的厚度為(58±2)納米。它在1300℃的干氧化條件下生長,在氮氧化物中進行後氧化退火。這種氧化物能夠阻擋高達20V的電壓。500納米厚的多晶硅被用作柵電極。它是通過低壓化學氣相沉積(LPCVD)製程在570℃下製造的,並摻雜有磷元素。在980℃進行合金化NiAl保證了n+和p+區的歐姆接觸。100納米鈦、700納米鋁和20納米鈦的堆疊順序在觸點處形成金屬化。

截止狀態下的電氣測量使用天然花生油作為設備表面頂部的外部鈍化,以防止測量機械手之間的電壓突變。在導通狀態下,柵極接20V電壓,源極和體接觸點接地GND。對於擊穿電壓測量(擊穿電壓VBD)測量時,要保持最大漏源電壓為1千伏,電流限制為100毫安(源極、柵極和體接觸點接地)。擊穿電壓被定義為1mA的源電流。

四,模擬程式

使用模擬工具Sentaurus·TCAD完成器件模擬。在應用程式SDE中設計建模,在應用程式SDevice中進行數值計算。參數文件由SDevice中內置的碳化硅、二氧化硅和多晶硅的默認工具參數組成。高斯注入剖面被認為是均勻的注入剖面。

對於導通狀態的研究,計算是對泊松方程的准穩態解進行旋轉對稱的。下面給出了兩個模擬模型。在一次模擬中,標記為「SimMob,I,Dit,Comp」。在Uhnevionak和Haucket等人之後,考慮了二氧化硅/碳化硅介面處的氧化物陷阱。固定氧化物的量由等效柵極氧化物的金屬氧化物半導體測試結構的C–V測量值確定。通過比較測量的和模擬的轉移特性來確定施主和受主類缺陷的數量。使用了以下參數:能級相對於導帶為50 meV、濃度為1×1012cm-3的施主類陷阱和能級遵循高斯分布、總密度為3.2×1015cm-2(eV)-1的受主類缺陷。TCAD模式正常用於介面屬性的計算。

此外,在注入鋁的p阱區考慮了基於缺陷的電荷補償。在以前的工作中顯示,高電荷補償是由注入鋁後產生深缺陷造成的。鋁注入層中的自由空穴密度在40%和80%之間顯著降低,這取決於鋁濃度。帶隙上半部分和帶隙下半部分的缺陷降低了鋁注入([鋁]≈1017–1018cm3)N型外延層([氮]≈1015 cm3)中的自由空穴密度。因此,在模擬時必須對p阱中的電荷平衡進行修改。然而,還不清楚補償因子是不是由氧化過程產生或引起的。由於不知道能量水平補償效應,所以沒有使用現有的效應模型,但是氮被插入到p阱區域。單孔減少了自由孔密度和補償,這是一個很好的例子。對於現有的LDMOS電晶體,在同一個p阱區,假設補償係數為60%,可以獲得模擬和測量的電晶體特性的最匹配。

然而,模擬的進一步優化也可能導致更低的補償因子和更高的類似施主的陷阱密度。SimMob,I,Dit,Comp的模擬只是作為一種可能的假設,所以鋁注入層和氧化層的補償因子並不廣為人知。

在第二個模擬模型「SimMob.Ⅱ」中,假設根據測量並忽略氧化物或體中的任何陷阱,溝道區中的遷移率是恆定值。

在截止下,模擬了無面積因子的低密度金屬氧化物半導體電晶體的晶胞。泊松方程計算的邊界條件是一個模擬路徑的電離積分值為1。數學計算將不會被定義為電離積分指數計算。在這裡,結合了Hatakeyama推薦用於4H-SiC功率器件的雪崩模型。

為了增加本徵載流子濃度,在穩態模擬期間器件溫度被設置為800 K,以便於模擬期間的數值收斂。因此,模擬和測量的泄漏電流不具有可比性。此外,必須考慮到,由於器件溫度升高,模擬擊穿電壓略微高估了約40 V。注意,這種對擊穿電壓的高估在大多數情況下不到10%,因此是合理的。此外,保持室溫會導致模擬在某些情況下會發生斷電情況斷電,從而導致測量錯誤。這也是300K晶格溫度模擬的工具故障載波產生的指示。

總的來說,氮注入區域的深層缺陷在模擬中沒有考慮。這是一個公開的在n-或者p型外延層的電荷補償效應,不會對自由電荷的相對密度產生重大影響。在p型外延層中突出的缺陷是HS1和HK4。Kawaharaet等人報告了p型外延層中進行鋁或氮注入([氮,鋁]≈7×1014 cm-3),隨後在1700℃退火後,注入濃度相關的低濃度HS1和HK4缺陷([Al]≈7×1015 cm-3) 。Laube等人公布了p型外延層([Al]1016cm-3)中注入氮濃度([N]1018cm-3)的約10%的補償比。氧化後,缺陷HK0出現。然而,據作者所知,還不清楚這種缺陷如何影響載流子壽命、薄層電阻以及它是不是氮注入層的電子陷阱。由於氮注入p型外延層中缺陷的影響相對較低或部分未知,RESURF區的器件模擬儘可能理想地進行。

五,電流–體積老化特性

圖2中給出了固態和非固態的電流-電壓測量值。這裡示例出了三個MOSFETs,其FPs、溝道和漂移長度分別為10、1–6和20μm。這些線代表模擬和測量的漏極電流曲線IDrain。對於模擬模型「SimMob,I,Dit,Comp」,考慮了近介面態和氧化物陷阱以及p阱區中基於缺陷的電荷補償,導致溝道區最初的4納米的溝道遷移率值為7至12 cm2/V·S。模擬結果與測量結果相差37%。這種差異可歸因於以下幾個現象:①注入氮層的RESURF劑量與模擬中預期的略有不同,②尚未優化的近介面陷阱和氧化物電荷模型,③六方和立方晶格位置上氮能級的分裂,這在模擬中沒有考慮,④在漂移區柵極氧化物頂部的FOX中沒有考慮氧化物電荷,⑤溝道積累的形成。

在模擬漂移區觀察到一個積累溝道,它降低了基態電阻。堆積通道的形成可能是一個真實的現象,但是很難估計它在各種器件中的擴展。轉移長度測量(TLM)在氮注入層獨立的測試結構導致在模擬值範圍內的電阻。由於這些測試結構在頂部有一個柵極氧化物和一個FOX,積累溝道的形成可能被認為是一個真實的現象。儘管如此,模型「SimMob,I,Dit,Comp」低估了測量值RON,這表明通道對器件總電阻的貢獻很大。在第二模擬模型「SimMob.Ⅱ」中,假設溝道區中的恆定電子遷移率為12cm2/VS的情況下。導通電阻與測量值吻合良好。在該模擬中,漂移層中的累積溝道被大大減小。

圖2(b)中描繪了截止狀態。模擬非常精確地預測了截止狀態下測量的雪崩值。值得注意的是,溝道長度為1和3μm的器件顯示出隨著阻斷電壓的增加,在納安至微安範圍內的測量漏電流的增加。在碰撞電離發生之前,通道較大的器件的漏電流在10-11和10-10A之間。對於短溝道來說,此處的短溝道會進一步通過RESURF區的2 μm重疊影響p阱,漏致勢壘降低會影響漏電流。此外,硅氧烷/碳化硅介面的介面張力被認為是高漏電流的原因。例如,正氧化物電荷可以增加溝道區的電子密度。此外,還觀察到,對於5V的柵極電壓,所有溝道長度測得的漏電流均約為1011A。因此,低密度金屬氧化物半導體電晶體通常與小溝道長度相結合。

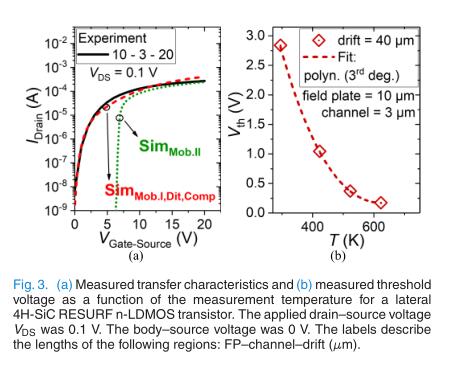

這種行為通過測量傳輸特性得到證實,如圖3(a)所示。固定的正氧化物電荷導致轉移特性向低電壓轉移。電荷在柵極和源極之間產生電位差,從而提高總柵極電壓。因此,特定量的正氧化電荷積累在測量值和模擬模型「SimMob,I,Dit,Comp」之間給出了很好的一致性。特別是模型的亞閾值區域。」SimMob,I,Dit,Comp」與測量值吻合。對於較高的柵極電壓,溝道和漂移區的電阻會影響曲線的曲率。模型」SimMob.Ⅱ」對於較高的柵極電壓非常匹配;圖3(b)給出了不同溫度下漂移長度為40μm的器件的測量閾值電壓。多項式擬合沒有用來擬合依賴於溫度的狀態電阻。目的是分別計算溝道和漂移區的電子遷移率。結果見第六節。

六,溝道遷移率和電阻

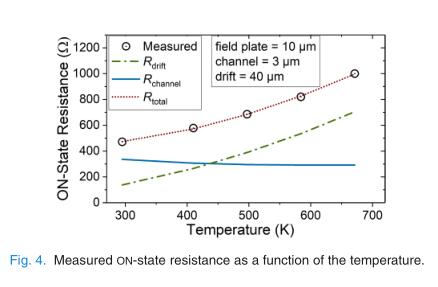

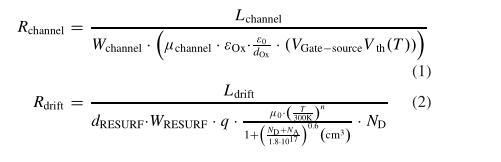

通道電阻似乎對總電阻有很大的影響。例如:用10μm的焦平面將漂移長度從40μm加倍到80μm,3μm的溝道分別得到結果為189兆歐姆·cm2和532兆歐姆·cm2。然而,漂移長度為40μm的溝道從3μm增加到10μm得到的結果分別為189兆歐姆·cm2和502兆歐姆·cm2。因此,溝道的微小變化將導致電阻率的強烈變化。所以,該溝道代表了RON的一個重要的組成部分。為了確定這一部分,進行了與溫度相關的測量。圖4顯示了狀態電阻與測量溫度的函數關係。對於FP長度為10μm、漂移長度為40μm、通道長度為3μm的器件,等式(1)和(2)表示測量數據的擬合函數,其中Rchannel和Rdrift分別表示通道電阻和漂移電阻。

其中,Lchannel1/LRESURF代表溝道/RESURF長度,Wchannel/WRESURF代表溝道/RESURF寬度,εox是二氧化硅的相對介電常數,dox表示氧化層的厚度,Ldrift代表漂移層的長度,Vth是器件的閾值電壓,ND/A是施主和受主的濃度,μchannel為溝道中的電子遷移率。閾值電壓的溫度特性通過單獨的測量來考慮,如圖3(b)所示。多項式擬合被用來推斷閾值電壓的數據和溫度的安全函數,如圖3(b)所示。在μ0 =1185 cm2/Vs,n=2,μchannel≈12 cm2/Vs時對應Rtotal,通過「SimMob,I,Dit,Comp」模型獲得在測量數據範圍內的溝道遷移率。因此,這個模型似乎能夠很好的擬合溝道區。此外,請注意,在400–500K的溫度範圍內,溝道電阻對總電阻的貢獻最大。對於更高的溫度,漂移區似乎是總電阻的主要部分。

七,導通與截止狀態

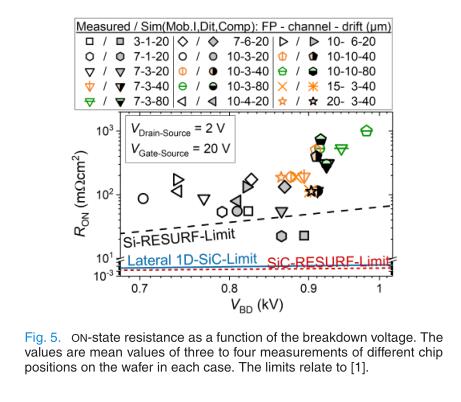

圖5概述了不同器件的模擬和測量電氣特性。它總結了漂移長度高達80μm的器件的RON是擊穿電壓VBD的函數。這些值是在每種情況下晶片上不同晶片位置的三到四次測量的平均值。下面是被測變數的一些特殊性質。

1)對於FP,溝道和漂移長度分別為10,10和80μm的情況,且最大擊穿電壓VBD為(981±17V)時,RON為(1098±6)兆歐姆·cm2。

2)對於較低的擊穿電壓VBD (823±42)V,對於3μm的FP和1 μm和20μm的小溝道和漂移長度,可以分別實現(55±0.3) 兆歐姆·cm2的電阻率。

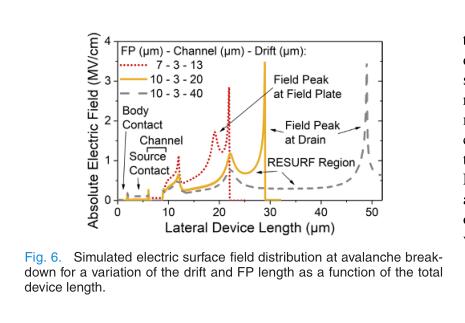

3)值得注意的是,擊穿電壓不表現出依賴於漂移長度的線性行為。這種非線性可能是模擬器件時由表面區域的電場分布引起的,如圖6所示。可以看出,平均電場強度並不總是成正比的。

4)此外,RON不隨漂移長度線性增加。為清晰起見,將該器件系列與7μm的FP、3μm的通道長度和(20、40和80)μm的漂移長度進行比較,如圖5所示。

這裡,根據漂移長度,RON的測量結果為(87、192和534) 兆歐姆·cm2。表面附近效應,例如溝道區或鈍化層的柵極氧化物處的氧化物/介面陷阱,可能是這種非線性的原因。

關於測量和模擬的比較,一般來說,模擬的VBD比測量的數據高,RON比測量的數據低。測量值與模擬值的差異導致平均偏差為11%,最差情況下最大偏差為41%。表面效應是在低於模擬預測的電壓下發生雪崩擊穿的一種可能的原因。圖5中描繪的模擬RON數據屬於模擬模型「SimMob,I,Dit,Comp」。通過該模型,可以重新調整溝道區的電特性,並調整測量和模擬的傳輸特性[參見第五節、第六節、圖2和圖3(a)]。對於通道長度小於1μm的器件,RON的模擬值與測量值相差58%。在通道長度大於3μm的情況下,RON的模擬值與測量值相差21%-43%。這些差異可能有幾個來源(見第五節)。在漂移區柵極氧化物上方的FOX中,不考慮氧化物陷阱是最有可能的。在模擬中觀察到漂移區中電阻降低的積累溝道的形成,在製造的器件中也是可能的。這種積累溝道的範圍無法估計。此外,假設注入的氮原子不完全激活的模擬降低了基態電阻,儘管這對於Simonka等人公布的90%-100%激活是不符合的。氮注入區(漂移區)中基於缺陷的電荷補償,其實際值為注入氮的10%–20%,不能單獨解釋RON的模擬值和測量值的差異。

因此,低輻射真實器件的解決方案包括氧化物缺陷的主動還原和近介面陷阱(氮處理或碳還原)。

八,設計指南和方向

儘管模擬和測量的RON絕對值有差異,但模擬和測量的RON和VBD,他們的設計變數遵循相同的趨勢。這允許總結一些設計準則。可以注意到電特性對設計變化的下列依賴性:1)溝道和漂移區的尺寸越大,RON越大;2)更

大的漂移區增強了VBD;3)更長的FPs降低了VBD,而對RON沒有任何影響。

最後,應考慮漂移長度超過20μm的單個器件完全由RESURF控制。否則,由於絕對電場的三角形分布,擊穿發生在源極和漏極之間,如圖6所示。在漂移長度較大的情況下,擊穿額外發生在垂直方向。這裡,RESURF劑量極大地降低了電場強度(見圖6所示)。此外,由圖6可見,在所有情況下,電場峰值出現在漏極控制擊穿。改進這種裝置的一個方法是主動減少磁場,例如,在漏極接觸周圍增加一個補償層(第二個RESURF區域)。

請注意「進一步模擬使用模型「SimMob.Ⅱ」,其不是基於電荷俘獲有關的物理現象,而是導致高的RON,並且在測量的和模擬的RON之間幾乎沒有差異,它可以提供深入了解的設計參數,以將VBD提高到1.2千伏,將RON降低到32兆歐姆·cm2。這裡,RERURF區域的劑量被提高到最佳RERURF劑量為6×1012cm-2,且注入深度被擴展到1μm。這導致器件在截止狀態下具有更高的魯棒性,同時RON降低。我們製造的和模擬的裝置的一致性證明了證明概念。我們的結果是最先進的,與文獻中報道的更複雜的RESURF設計非常相似。根據所需的功能,對於80μm的大漂移區和10μm的溝道長度,可以獲得VBD為981 V,對於1μm的小溝道長度和20μm的漂移長度,可以獲得53 兆歐姆·cm2的RON。雖然我們的值超過了硅-RESURF限值,但對於4H-SiC n-LDMOS電晶體,FP為3μm、溝道長度為1μm、漂移長度為20μm的電晶體會產生12.3 MW/cm2的品質因數(FOM),這是最先進的。Noborio等人顯示具有兩個RESURF區的器件為43 MW/cm2。然而,我們的器件製造更簡單(只有一個額外的光刻步驟和注入),它允許直接集成到20伏碳化硅互補金屬氧化物半導體技術。

九,結論

提出了一種具有集成到先進的20V 4H-SIC CMOS製程中的能力的可生產的RESURF n-LDMOS電晶體。通過僅使用一個額外的注入步驟,電荷補償層被引入電晶體,這允許更高的擊穿電壓。不同設計的器件的電學特性與數值模擬結果高度一致,尤其是在截止態方面。在導通狀態時,模擬表明,電阻主要由模擬中未優化的參數決定,例如氧化物陷阱。導致電阻升高的主要部分似乎是溝道區和低電子遷移率。然而,所預製器件的電學和數值特徵可以預測,對於FP為3μm、溝道為1μm、漂移長度為20μm的器件,更高的RESURF劑量約為6×1012cm2將導致43 MW/cm2的FOM值。漂移長度減少到13μm時,FOM的值甚至可以達到52 MW/cm2。