包含多個矩形的Pblock

- 2019 年 10 月 30 日

- 筆記

pblock是否可以嵌套

Pblock是可以嵌套的,儘管這種應用方式並不常見。嵌套Pblock是為了更細粒度的對相關邏輯進行布局約束。從設計層次角度講,嵌套的Pblock對應的邏輯單元是父層與子層的關係。

看下面一個例子。模組arnd1和模組transformLoop[0].ct關係如下圖所示。對這兩個模組分別畫Pblock,得到pblock_arnd1和pblock_transformLoop[0].ct,這兩個pblock是嵌套的。

對於嵌套的pblock,它們在Physical Constraints窗口中也是按層次方式顯示的,如下圖所示。這樣就可以清晰且直觀地看到pblock的關係。

嵌套的兩個pblock,它們的一些屬性是不相同的。最典型的是PARENT不同,如下圖所示。頂層的pblock其PARENT值為ROOT,而子層的pblock其PARENT是頂層的pblock。

pblock是否可以包含多個矩形

Vivado還支援創建多個矩形構成一個pblock,從而使得該pblock形狀不是矩形。這在某些場合是非常有用的。相應的操作非常簡單。

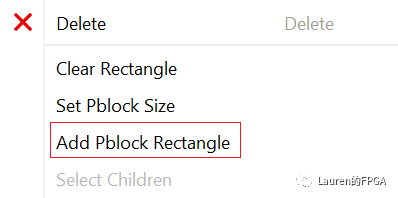

首先,對指定的cell創建一個pblock;其次,在Device View中選中該pblock,點擊右鍵,選擇Add Pblock Rectangle,如下圖所示。此時會創建一個新的矩形。這兩個矩形共同構成一個新的pblock。可以反覆選中pblock,點擊右鍵添加多個矩形pblock,從而形成多個矩形pblock共同構成一個非矩形的pblock。

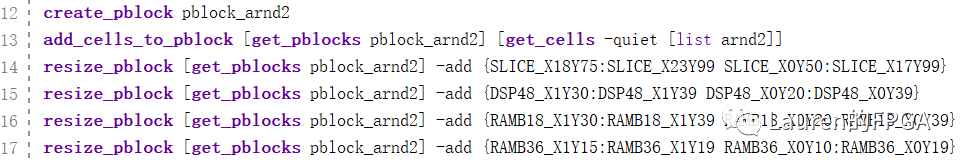

對於多個矩形構成一個pblock的情形,這些矩形之間會以虛線形式連接,表面它們隸屬於同一個pblock。如下圖所示。從Tcl命令角度講,無非是增加了幾行resize_pblock命令而已。

pblock是否可以佔據整個Clock Region

此外,pblock的大小可以是整個時鐘區域(Clock Region,包括相應的IO Bank)。只需要在畫pblock時,將整個時鐘區域框住即可,如下圖所示。

此時,相應的Tcl命令就很簡單,可以看到只需要一條resize_pblock命令即可確定pblock的大小和位置。實際上,在SSI晶片設計中,給每個die畫一個大的pblock時(整個Pblock將整個die包含其中),只用指定左下角和右上角的時鐘區域坐標即可。