CMOS設計手冊—基礎篇

- 2020 年 9 月 5 日

- 筆記

- CMOS設計手冊總結

模擬CMOS

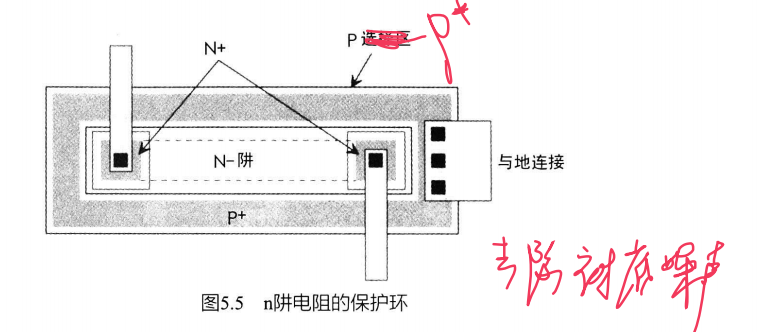

- 襯底雜訊:由於相鄰的電阻互相注入電流而產生的襯底雜訊。解決方法:在兩個電阻之間加入一個P+注入區(作為P襯底晶圓的襯底接觸)。P+注入區保護電路免受載流子的影響,由於注入區是一個環形,所以成為保護環。

-

共質心版圖

共質心(共同的中心)版圖有助於改善兩電阻之間的匹配性能(代價是兩元件之間具有不均勻的寄生特性),另外,共質心也能改善MOS和電容的匹配性能。

3.MOS電容

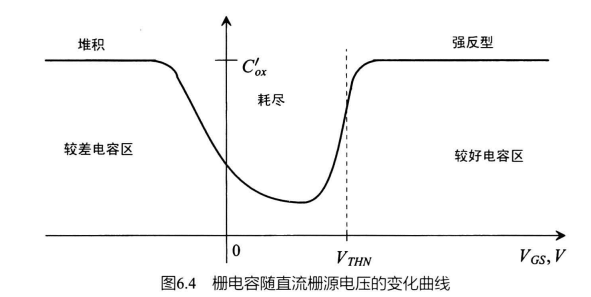

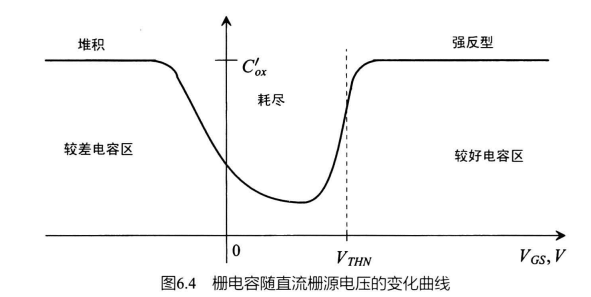

- 堆積 (VGS<<Vth)

當VGS<0,來自襯底移動的空穴被吸引(堆積)到柵氧層的下方。當MOS管處於堆積區時,柵極到地的電容Cgb的主體部分經過了襯底的大寄生電阻。為了讓MOS工作在吃工作區,需要在柵氧化層周圍有足夠的襯底連接(以減少寄生襯底電阻)。從柵極到gnd之間的電容之和為:

\]

-

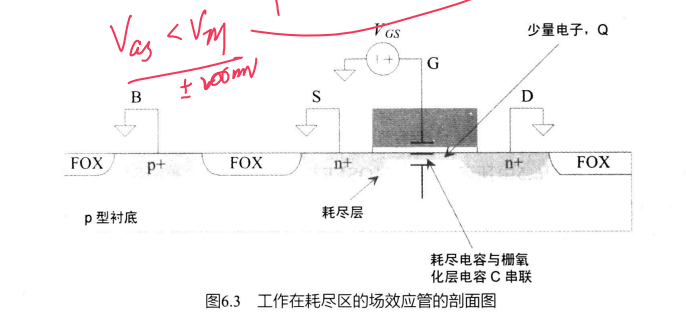

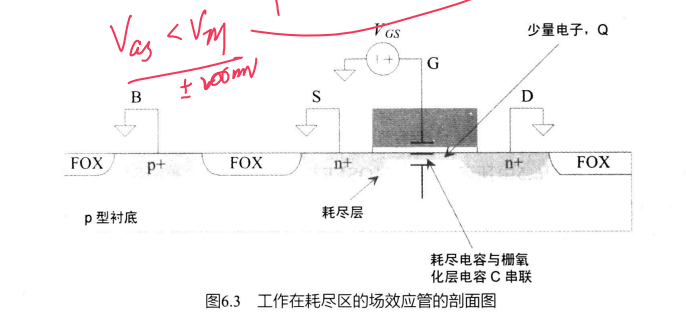

耗盡 (VGS<VTH)

當VGS<Vth(大約小於100mV),此時VGS不夠負,不能吸引大量的空穴到柵氧層的下方,同時也不能足夠正,無法吸引大量的電子。此時的柵極下方的硅表面被稱作近耗盡(自由電子和空穴被耗盡),觀察下圖,當

VGS從某個負電壓開始上升,柵極下方的空穴將會被替代,只留下不能移動的受主離子提供一個負電荷。隨著VGS的增加,柵氧層下方感應的n溝道和三級之間將存在一個電容。同時在耗盡溝道和襯底之間還會存在一個耗盡電容。柵極和源極/漏極的電容只是覆蓋電容,而柵極和襯底之間的電容是由氧化層電容和耗盡層電容串聯而成的。下圖中的耗盡電容式由n溝道和襯底之間形成的。由於氧化層下方的表面不是重n+區,所以工作在這個區的MOS被稱為弱反型區或者亞閾值區

-

強反型區 (VGS>>vth)

當VGS>>Vthn時,大量的電子被吸引到柵極下方,此時柵氧化層表面稱為反型,即不再是P型了。當需要一個電容時,可以最好時MOS工作在強反型區,被吸引之柵氧化層下方的電子將漏極和源極短接在一起形成電容的低電阻底板(常將源漏相連來講MOS做電容)。

耗盡型器件(負的閾值電壓,閾值電壓等於0時,器件導通)

增強型器件(正的閾值電壓,VGS=0時,器件截止)

4.MOSFET的I/V特性

-

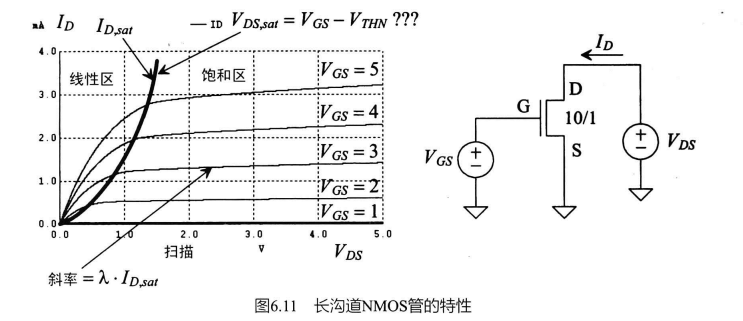

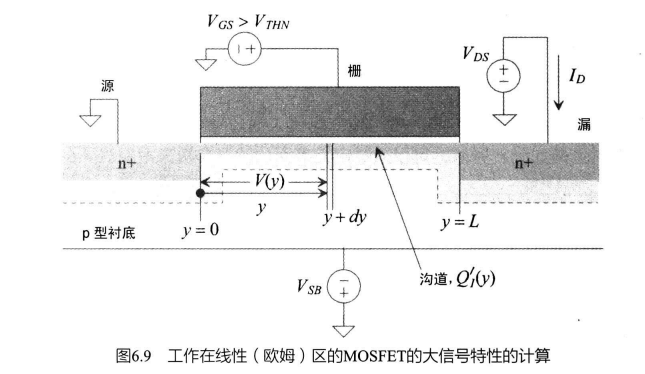

線性區(Vgs>Vth,Vds<Vgs-Vth)

由於Vgs>Vth,所以在柵氧化層下的表面會反型,因為Vds>0,所以有漂流電流從漏端流向源端。

\]

-

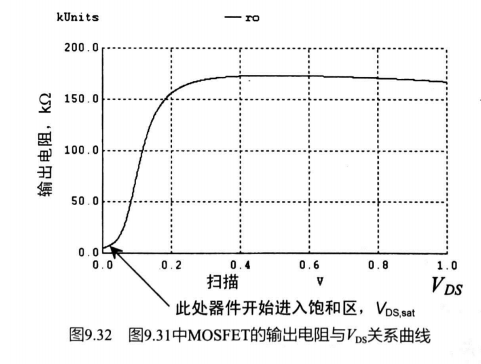

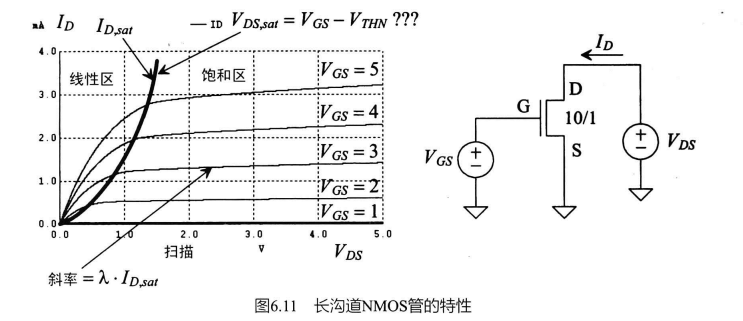

飽和區(Vgs>Vth,Vds>Vgs-Vth)

當Vds=Vgs-Vth時,柵電極下方(漏極與溝道的匯合處)溝道中的反型電荷為零,這個漏端和源端之間的電壓被稱為Vds,sat=(Vgs-Vth),它表明溝道在漏端和溝道交界處被夾斷。增加Vds並超過Vds,sat,會將固定電荷吸引至漏端,從而使得溝道中緊臨漏端的電荷被耗盡。繼續增加並不會使漏端電流繼續增加(由於溝道長度調製效應會使漏端電流隨著漏端電壓增加而增加)

\[I_D=\frac {1}{2} β(V_{GS}-V_{TH})^2(1+λV_{DS}) ,λ=\frac {1}{L}\frac {dX}{dV_{DS}}

\]遷移率會隨著Vds變化而變化,

- 飽和區中的Cgs計算:

\[C_{gs}=\frac {2WLC_{ox}}{3} ,C_{ox}=\frac {E_{ox}}{t_{ox}}

\]

- 飽和區中的Cgs計算:

-

溝道長度調製效應和體效應效應

溝道長度調製效應:當柵和漏端之間的電壓差減小時,實際的反型溝道長度在減小,這稱為溝道長度調製效應。

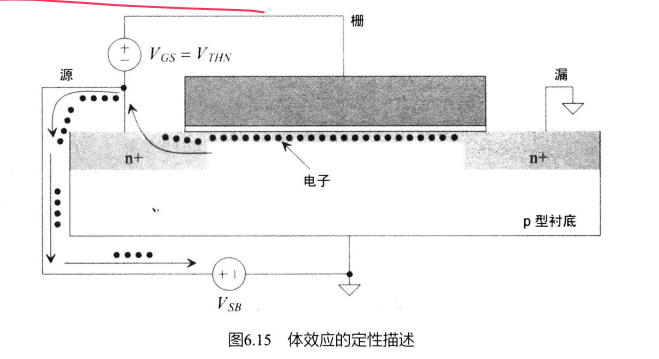

體效應:當\(V_{SB}\)開始增加時,閾值電壓也開始增加,這被稱為體效應。電子從溝道中被吸引到了\(V_{SB}\)的正端,為了保持表面反型,必須要在mosfet上施加一個更大的\(V_{GS}\)。於是從溝道中獲取電子帶來的效果就是MOSFET的閾值電壓增加了。

- 亞閾值電流(\(V_{GS}<V_{TH},小於大概200mV以內\))

MOS並非完全關閉,而是會有一個非常小的漏電流存在,該電流被稱為亞閾值電流。當MOS管工作在這個弱反型區區域,也稱工作在亞閾值區。困擾工作在亞閾值區的·電路主要是匹配、雜訊、頻寬。例如:由於漏電流和柵源電壓呈現指數關係,這些電壓的任何不匹配都會引起漏電流的大變化。

\]

短溝道MOSFET(L<1μm)

- 載流子速度飽和:在MOSFET溝道與漏端之間的載流子速度會達到飽和。

- 速度過沖:在尺寸非常小的器件中,在漏端附近漂移的一些載流子能獲得比平衡條件下載流子的熱能大的多的能量。這些載流子被稱為熱載流子。熱載流子的散射不在被局域化,這允許它們有著比上面遷移率更高的遷移率。載流子的速度可以超過上圖所示的飽和速度。這種效應稱為速度過沖,它能提高MOSFET的速度和跨導(有益),但是熱載流子也能隧穿柵氧化物引起柵電流或被柵氧化物俘獲,結果是改變了MOSFET的閾值電壓,同時熱載流子還能引起碰撞電離(雪崩倍增:當反偏的PN接面中電場變得非常大時,載流子被加速至能夠從晶格中撞出更多的電子—空穴對,這將導致二極體電流的增加。這一附加電流的產生被稱為雪崩倍增。)

MOS縮比

- MOSFET的溝道長度可以用按比例縮小(縮比)理論描述。縮比參數S<1,

\]

\]

\]

- 縮比的好處:

- 更小的器件尺寸,從而減少了晶片面積

- 更低的柵延遲,允許器件在更高的頻率下工作

- 降低功耗(降低了電壓電壓)

短溝道效應

當電場強度達到一定值時,速度將達到飽和值,也就是說速度不在隨電場的增加而增大。電子的漂移速度與施加的電場的比值就是電子的遷移率:

\]

超過臨界電場,遷移率開始減小,工作在飽和區(柵氧化層下方的短溝道交界處的電荷量為零,並且溝道被夾斷)時短溝道MSOFET的漏電流變化:

\]

工作在飽和區的短溝道MOSFET的漏電流隨著\(V_{GS}\)線形增加,而長溝道理論表明漏電流隨著\(V_{GS}\)呈現平方率關係

- 負偏置溫度不穩定性(NBTI)

在現代PMOS器件中,當柵電壓低於源電壓(\(V_{SG}<0\))時,會觀察到器件的關鍵參數如閾值電壓隨著時間漂移。一直以來,俘獲在氧化物中的空穴的脫離及介面態的產生認為是其原因。NBTI在NMOS中也存在,但是在PMOS中更明顯。

-

氧化層擊穿:為了保證器件的可靠性,穿過器件柵氧化層的最大電場應當限制在10MV/cm.

-

漏致勢壘降低(DIBL):漏端和源端之間加上電壓後,漏端感應勢壘的·降低會使閾值電壓下降。在漏端施加的正電壓有助於將電子吸附到柵極氧化層下方,柵極所需的電壓減小,閾值電壓降低。由於閾值電壓隨著\(V_{DS}\)的增加而減小,結果導致漏電流增加,從而減少了MOSFET的輸出電阻。

- 柵致漏電流泄露(GIDL):GIDL用來描述漏端到襯底的泄漏電流。當器件工作在堆積狀態(\(V_{GS}<0\),假設NMOS器件的柵為地電位),表面和襯底電勢幾乎相等。在這種情況下,當漏端處於較高電勢時,雪崩倍增或帶間的隧穿加劇,柵極下方的少數載流子被掃至襯底而形成泄漏電流。

- 柵隧穿電流:隨著柵氧化層厚度按比例縮減,直接隧穿通過柵的載流子的幾率越來越高,形成柵電流。

電雜訊分析

雜訊類型:

-

由於電荷在導線或者器件中的離散隨機運動而引起的雜訊(稱為電路固有雜訊,如熱雜訊、散粒雜訊、閃爍雜訊等)

-

量化雜訊(有模擬訊號轉化為有限字長的數字雜訊)

-

耦和雜訊(由臨近電路間的相互饋通或者干擾而引起的)

熱雜訊

電阻的雜訊主要是電子在熱效應作用下隨機運動的結果。這種類型的雜訊就是熱雜訊,也叫約翰遜雜訊。電阻的熱功率可以有功率譜密度表徵:

\]

- 積分雜訊

此電路唯一能產生雜訊的元件是電阻。電阻產生熱雜訊。電阻的雜訊頻譜密度為\(\sqrt{4KTR}\),於是輸出雜訊頻譜密度為:

\]

由於\(V_{onoise,rms}(f)=\sqrt{NEB\times V_{onoise}(f)}\),所以輸出雜訊電壓的均方值為

\]

此電路中的熱雜訊均方根值受到電容大小的限制,與電阻大小無關

- 散粒雜訊

散粒雜訊是由電荷穿越勢壘(比如二極體)的離散運動造成的。功率譜密度:

若要出現散粒雜訊,必須要有勢壘和流動的電流。散粒雜訊在長溝道MOSFET不會出現。由於柵隧穿電流的存在,在短溝道MSOFET中就會出現散粒雜訊。當一個長溝道MOS工作在飽和區時,進入溝道和漏極之間耗盡區的電荷具有離散性。但是這種離散運動是由MOSFET溝道電阻的溫度變化引起的,而不是由穿越勢壘並被電場清掃乾淨的載流子引起的。

-

閃爍雜訊

閃爍雜訊是一種低頻雜訊,也叫粉紅雜訊(出現在可見光譜中較低頻段的淡紅色光或者1/f雜訊)

模擬設計模型

長溝道模型

體效應跨導

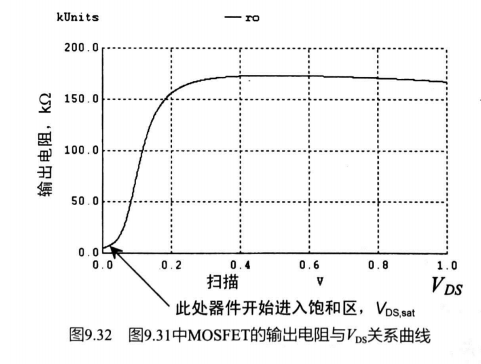

輸出電阻

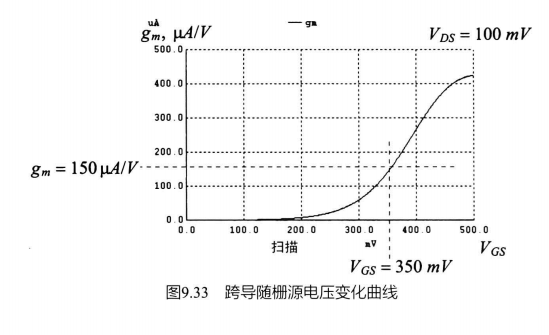

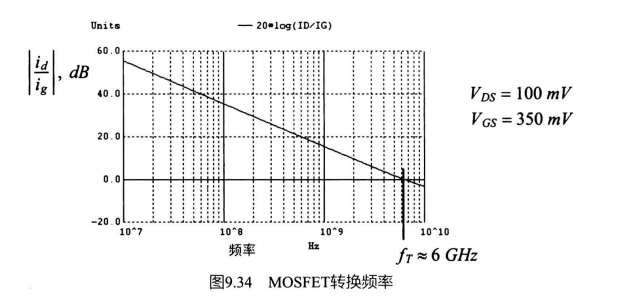

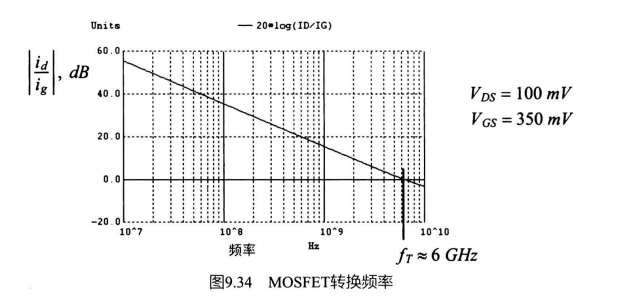

MOS管的轉換頻率\(f_T\)

PMOS的轉換速度比NMOS慢,因為空穴遷移率比電子遷移率低。**對於短溝道MOSFET,遷移率μ不再是一個常數,隨著溝道長度的縮短(μ=v/E,增強了漏端和溝道長度的電場強度)開始下降,因此將μ/L看做一個相對不變的常數,因此對於短溝道:

因此為了高的速率,需要採用儘可能小的溝道長度和儘可能大的過驅動電壓。

模擬設計的通用器件尺寸

- 對於2通用的模擬設計,採用的L一般為最小值的2~5倍。在模擬設計中,採用的L為2倍,作為在速度和增益之間的一個較好的折中。

- 對於通用設計,採用的\(V_{GS}-V_{th}\)一般為VDD的5%

**亞閾值$ g_m\(和\)V_thn$ **

當MOS工作在亞閾值區時,跨導隨著偏置電流增加而線性增加,**但是工作在亞閾值區的MOS的速度\(f_T\)相當低。小電流對器件自身電容的充電將它的速度小於MHz.隨著CMOS縮小,MOS本身的固有速度提高了。因此增加了工作在亞閾值區的設計。

溫度效應

隨著溫度變化的是遷移率和閾值電壓

遷移率隨著溫度上升而減小。

隨著溫度的上升,\(V_{th}\)和μ都會減小,遷移率μ的減小將使得\(I_D\)減小,而閾值電壓\(V_{TH}\)的減小,使\(I_D\)增大。在低\(V_{GS}\)處,閾值電壓的變化起主要作用,漏電流隨著溫度上升而增加。而在高\(V_{GS}\),遷移率的變化其主要作用,漏電流隨著溫度上升而降低。當這些效應相互抵消時,漏電流不隨溫度變化

短溝道MOSFET

-

輸出電阻

-

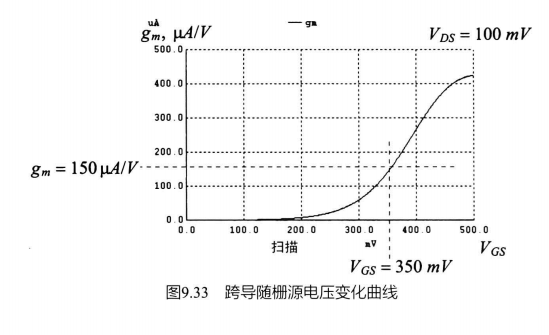

正向跨導

-

轉換頻率

專用設計

注意上式與漏電流無關,它完全是基於MOSFET的溝道長度和遷移率的,它表明了如果增益增加,速度就會下降。**對於短溝道MSOFET,GFT只單獨依賴於遷移率(短溝道下,遷移率會下降,μ/L相當於不變常數。MOSFET的\(f_T\)與L成比例,而不是與\(L^2\)成比例。

對於工作在強反型的器件,增益為以下式子,該式子表明增益會隨著漏電流增加而減小

以下式子表明開環增益會隨著L的增加或者\(V_{GS}\)的減小而增大。

當MOSFET工作在亞閾值區(弱反型區)時,可寫出:

上式表明長溝道MOSFET工作在亞閾值區時,增益與漏電流無關。

短溝道MOSFET的開路增益要比長溝道的開路增益要低的多,但是器件越小對高速設計越好,因為器件的\(f_T\)較高。一般而言對於高速設計採用小尺寸製程,對於低頻設計採用較老的CMOS製程。

MOS雜訊模型

-

漏電流雜訊模型

mosfet的雜訊是由熱雜訊和閃爍雜訊引起的。由溝道電阻,其模型是飽和區電阻為\(\frac {3}{2g_m}\)然後積分得到,不考慮面積關係,線性區電阻為\(R_{ch}\),引發的MSOFET在飽和區的熱雜訊可用功率譜密度PSD表示為

\[I_R^2(f)=\frac {4KT}{\frac {3}{2g_m}}=\frac {8kTg_m}{3}

\]此雜訊電流源跨接了MOSFET的漏端和源端。

-

閃爍雜訊

閃爍雜訊(1/f雜訊)是由於電荷在氧化層/半導體介面被俘獲造成的,只要在非連續的材料中有直接電流流過就會有閃爍雜訊出現。閃爍雜訊模型可用PSD表示:

\[I_{1/f}^2(f)=\frac {KFI_D^{AF}}{f(C_{ox}L)^2}

\]

MOS的漏電流雜訊總PSD寫作:

MOS的輸入相關雜訊PSD寫作:

在較老的CMOS技術中,比如說350nm和更早技術時代,n型多晶硅用來形成NMOS和PMOS器件的柵(單功函數柵極)。這使PMOS器件的溝道免於直接在柵氧化物下方的表面形成,反而會在器件中形成一個掩埋型溝道。這樣避免了電流在氧化物和半導體表面傳導,還避免了載流子的俘獲和隨機釋放,而後者是MOSFET的漏電流閃爍雜訊的主要組成部分。其結果是在較老的幾代CMOS製程中,PMOS器件相比NMOS器件有著相當好的雜訊性能。

在現代製程中,n型多晶硅用來形成NMOS器件的柵,而PMOS器件的柵是採用的P型多晶硅。結果是兩種器件都用的表面溝道,因此此時採用PMOS器件優勢就消失了,而NMSO器件大的gm在低雜訊設計成為首選器件。