一分鐘理解系列—半導體存儲晶片的知識點總結

在電腦的存儲器中,按存儲介質進行分類的話,可將存儲器分成半導體存儲器、磁表面存儲器、磁芯存儲器、光碟存儲器。而除了半導體存儲器中的數據易失以外,其他的存儲介質都具有非易失的特性。

那麼,半導體存儲晶片的結構是怎樣的呢?

話不多說,我們來看下吧。

半導體存儲晶片的基本結構

半導體存儲晶片由解碼驅動電路、存儲矩陣、讀寫電路、地址線、數據線、控制線、片選線組成。其中,解碼驅動電路、存儲矩陣、讀寫電路屬於核心結構。

存儲矩陣用來存儲0/1程式碼,地址線、數據線主要用來連接CPU和外部設備。現在假設CPU或者外部設備給出地址,表示要存/取的數據在存儲矩陣的哪個存儲單元中,然後經過解碼驅動電路,選擇對應的存儲單元,從而完成存/取數據。

地址線是單向的,由CPU指向存儲器,或者由I/O設備的控制器指向存儲器。數據線是雙向的。由地址線和數據線可以計算出晶片的容量。那麼如何計算呢?感興趣的朋友可以閱讀之前的這篇文章。吐血整理!這篇帶你徹底理解主存中存儲單元地址的分配

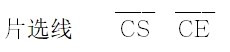

片選線,也叫做晶片選擇訊號,指出這次存/取操作給出的地址是不是這個存儲晶片的地址。半導體存儲晶片的片選線一般有兩種標識方式,表示方式如下所示:

CS(晶片選擇訊號),CE(晶片使能訊號),低電平表示有效,高電平表示無效,也就是說,如果片選線訊號為低電平,則表示想要存/取的數據位於片選線所在的晶片中。

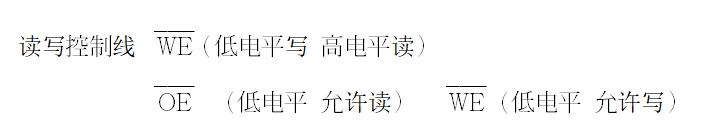

讀寫控制線,表示這次對半導體晶片的操作是讀操作還是寫操作。可以用一根線或者兩根線表示,用一根線表示的話是WE,用兩根線表示的話是WE和OE,具體如下所示:

存儲晶片片選線的作用

接下來我們來詳細討論下存儲晶片中,片選線的作用。

假設CPU現在要求用16K×1位的存儲晶片組成64K×8位的存儲器。如何用16K×1位的存儲晶片組成64K×8位的存儲器?

我們用圖來看下,實際上這個問題解決並不難

16K×1表示存儲容量,每個存儲單元存儲1位的0/1數據。那麼,我們用8個這樣的晶片,對8個晶片相同的地址同時進行操作,每個晶片給出1位,8個晶片就構成了16K×8的存儲器。

但是,CPU要求的是64K?這個應該怎麼做?

實際上,也不難,每8個晶片分成1組,然後複製4組,就構成了64K×8的存儲器。

在進行讀寫操作時,8個晶片是同時進行工作的,所以,他們的片選線是連接在一起的。

然後對64K的空間進行劃分,所以CPU的地址中0-(16K-1)的地址分配到第一組的晶片中,16K-(32K-1)的地址分配到第二組的晶片中,32K-(48K-1)的地址分配到第三組的晶片中,48K-(64K-1)的地址分配到第三組的晶片中分配到第四組的晶片中。

現在假設訪問的地址是65535,進行寫操作,那麼這個地址表示的存儲晶片應該在最後一組中,片選訊號看到這個地址後,就會選擇最後一組,其他三組晶片對應的片選訊號是無效的,就是高電平,最後一組對應的片選訊號是有效的,也就是低電平,數據就會保存在最後一組的存儲晶片當中。

半導體存儲晶片的解碼驅動方式

解碼驅動電路的作用是:在給出地址之後,根據這個地址取找到這個地址對應的存儲單元。

而半導體存儲晶片的解碼驅動方式有兩種:線選法,重合法。

我們先來看下線選法

線選法

在上圖中,有A0-A3的4位地址,那麼24表示有16個存儲單元,那麼每個存儲單元可以存儲多少位?圖中給出的數據線是從D0-D7,一共8位。綜合起來,就表示這是一個16K×8的存儲器。

如何進行選擇?

在上圖中,地址解碼器輸入的是4根線,輸出的16根線。給定一個輸入,在輸出這一端,只有一根線是有效的,只有一根線上的訊號會控制相應的存儲單元中的所有存儲元件進行數據的輸入或者輸出操作。

那麼在讀寫控制電路中,如果是讀選通,就會將數據矩陣中的數據進行對外輸出;如果是寫選通,就會將數據寫入到矩陣中的存儲元件中。

現在,來看下具體工作過程:

假設地址解碼器給出的地址是全0,進行解碼過後,只有0這根線是有效的,其他的都是無效的。現在進行的是讀操作,那麼就會控制讀/寫控制電路打開,使得數據可以從存儲矩陣輸出到數據匯流排上。只有給定的單元才可以進行輸出。

那麼,線選法有沒有缺點呢?缺點是什麼?

在上圖的解碼中,地址線是4根,容量是16K×8,現在的電腦存儲器,並不存在這麼小的容量。

現在假設有1M×8的存儲晶片,地址線有20根,經過解碼器解碼後就有1M條線,每給出一個地址,1M條線中,只有一條有效。而1M條線,就是1000000條線,做在晶片中將會非常密集,這麼高的集成度很難做到。

所以,線選法對於容量很大的存儲器來說,是個不好的方法。

接下來,來看下重合法

重合法

在線性法中,存儲單元的布局方法是一個線性的數組;而在重合法中,存儲單元的布局方法是二維的數組。

在重合法中,將地址分成了兩部分,一部分是X,另一部分是Y,也可以叫做行列地址。行列地址分別進行解碼,只能有一根線是有效的。具體工作過程:

假設給出的行列地址都是全0,行列地址進行解碼後只有(0.0)這條線是有效的。只有這條線上的存儲單元被選中。那麼這時候,Y0這條線上的開關就會打開,數據就會通過這個開關進行數據輸出。在這個過程當中,X0上的除了Y0上的存儲單元的數據會進行輸入以外,其他的存儲單元上的數據一樣會進行輸出,但是,當數據經過Y31線上的開關時,由於這條線是無效的,數據會被攔截,所以,數據就輸出不了,所以數據沒有到數據線去。那麼Y0上的除了X0的存儲單元的數據會進行輸入以外,其他的存儲單元上的數據一樣會進行輸出,同樣的道理,就不另外解釋了。

那麼,重合法的優點是什麼?

在上面的線選法中,我們是假設有1M×8的存儲晶片,地址線有20根,用線選法的話,經過解碼器解碼後就有1M條線。那麼,同樣的大小,我們採用重合法的話,地址線就分成兩部分,每一部分都是1K條線,總計就是2K條線,那麼,就比線選法進行解碼的1M條少很多了,這樣子,晶片就能做到很高的集成度。

結語

講了那麼多,不知道各位是不是清晰的理解了呢哈哈?