Verilog程式碼和FPGA硬體的映射關係(五)

- 2020 年 5 月 26 日

- 筆記

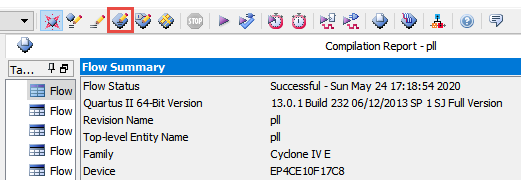

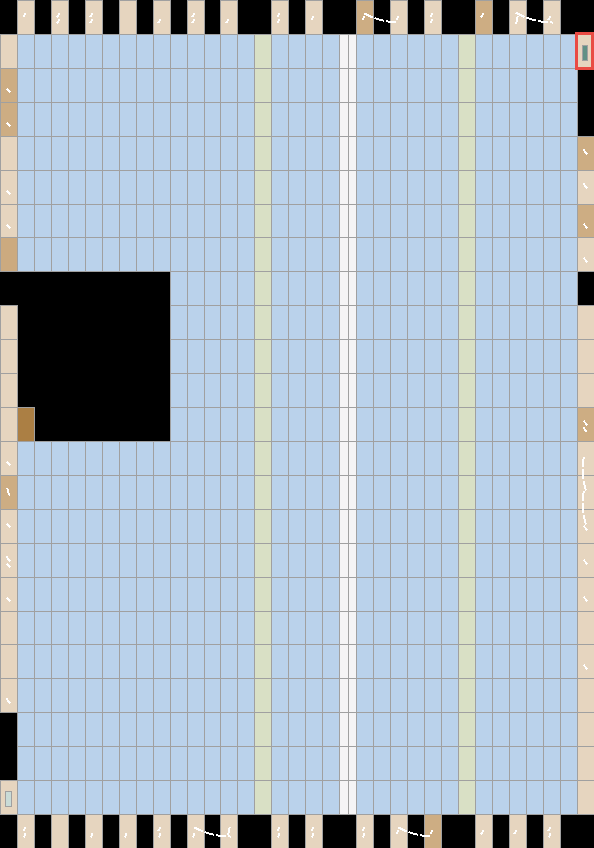

既然我們可以指定暫存器放在IOB內,那我們同樣也可以指定PLL的位置。首先要確保我們有多個PLL才行。如圖1所示,我們所使用的EP4CE10F17C8晶片剛好有兩個。

圖 1

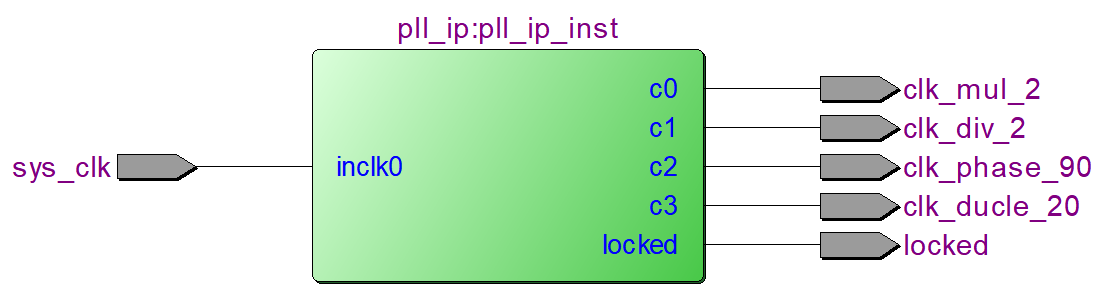

為了演示這個例子,我們使用pll工程,RTL程式碼如下所示:

1 //-------------------------------------------------- 2 module pll( 3 input wire sys_clk , //系統時鐘50MHz 4 5 output wire clk_mul_2 , //系統時鐘經過2倍頻後的時鐘 6 output wire clk_div_2 , //系統時鐘經過2分頻後的時鐘 7 output wire clk_phase_90 , //系統時鐘經過相移90°後的時鐘 8 output wire clk_ducle_20 , //系統時鐘變為占空比為20%的時鐘 9 output wire locked //檢測鎖相環是否已經鎖定,只有該訊號為高時輸出的時鐘才是穩定的 10 11 ); 12 13 //------------------------pll_ip_inst------------------------ 14 pll_ip pll_ip_inst( 15 .inclk0 (sys_clk ), //input inclk0 16 17 .c0 (clk_mul_2 ), //output c0 18 .c1 (clk_div_2 ), //output c1 19 .c2 (clk_phase_90 ), //output c2 20 .c3 (clk_ducle_20 ), //output c3 21 .locked (locked ) //output locked 22 ); 23 24 endmodule 25 //-------------------------------------------------

程式碼編寫完後依然需要點擊「Start Analysis & Synthesis」圖標進行分析和綜合。然後雙擊「Netlist Viewers」下的「RTL Viewer」查看RTL視圖。

圖 2

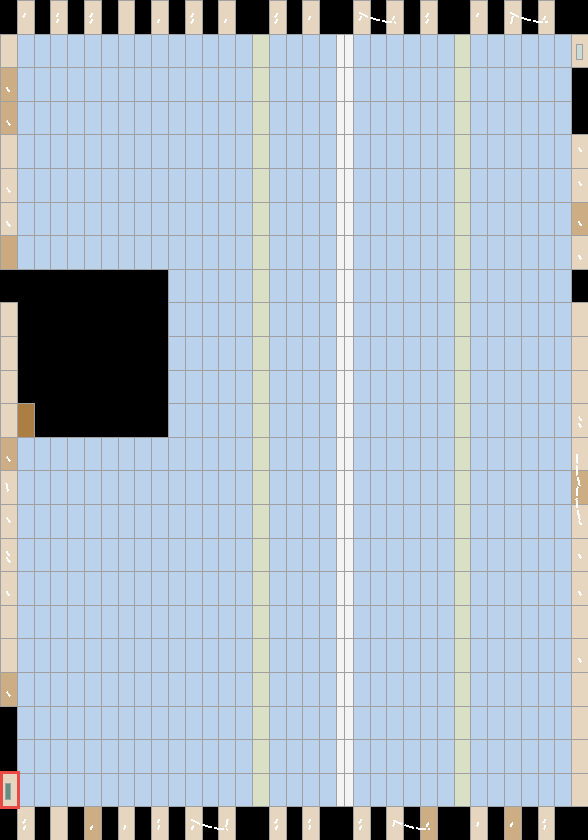

點擊「Start Compilation」圖標全編譯進行布局布線,然後打開Chip Planner視圖。Chip Planner打開後的介面如圖3所示,我們可以看到在版圖模型中左下角有一塊顏色變深的區域,與之形成鮮明對比的是右上角顏色沒有變深的位置,這就是我們FPGA晶片中兩個PLL的位置,而顏色變深的區域說明資源被佔用。

圖 3

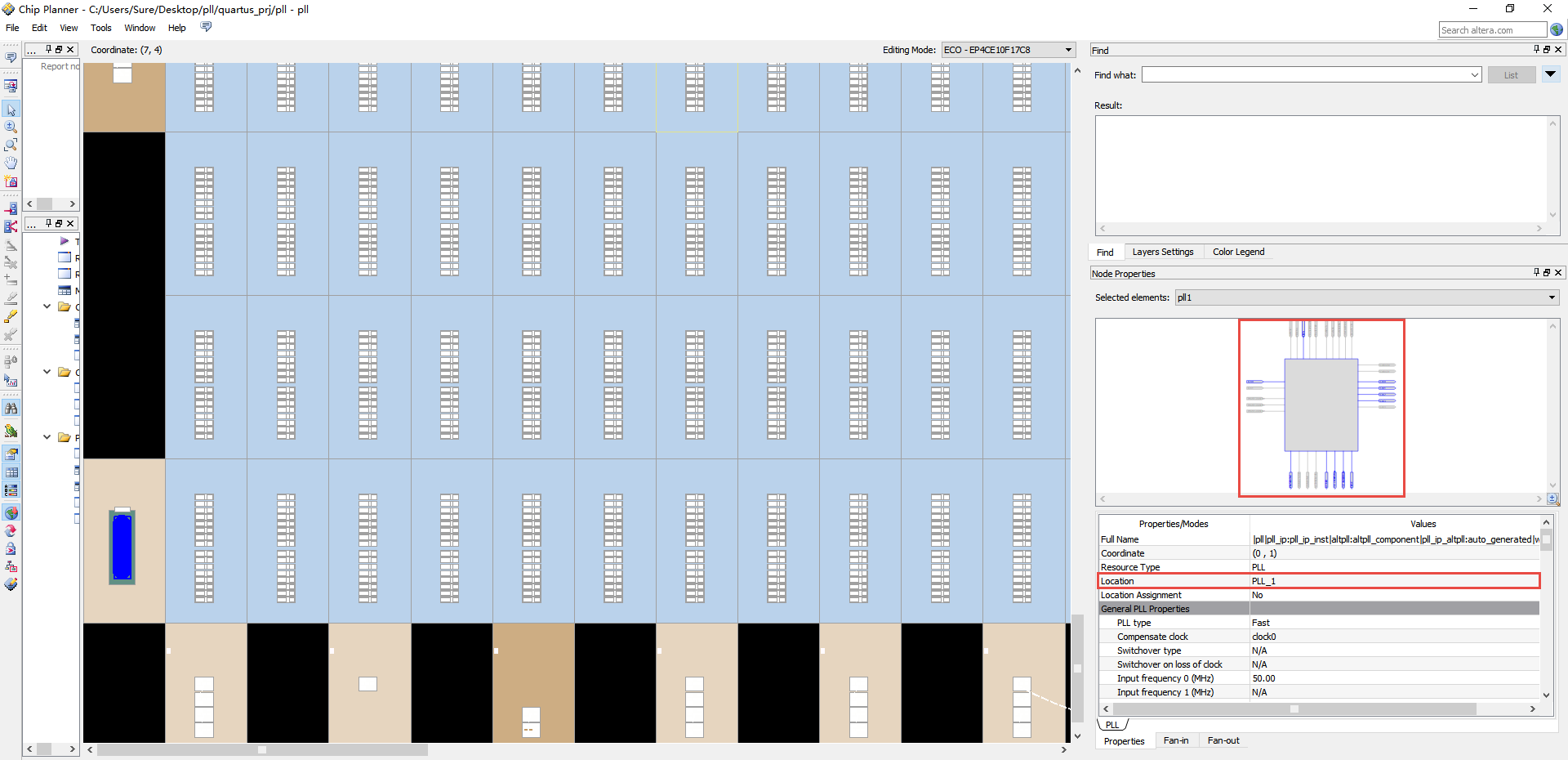

放大並點擊該PLL,如圖4所示,可以在右側看到該PLL的結構圖中顯示的部分藍色高亮訊號,下面「Location」則顯示了該PLL的名字為「PLL_1」。

圖 4

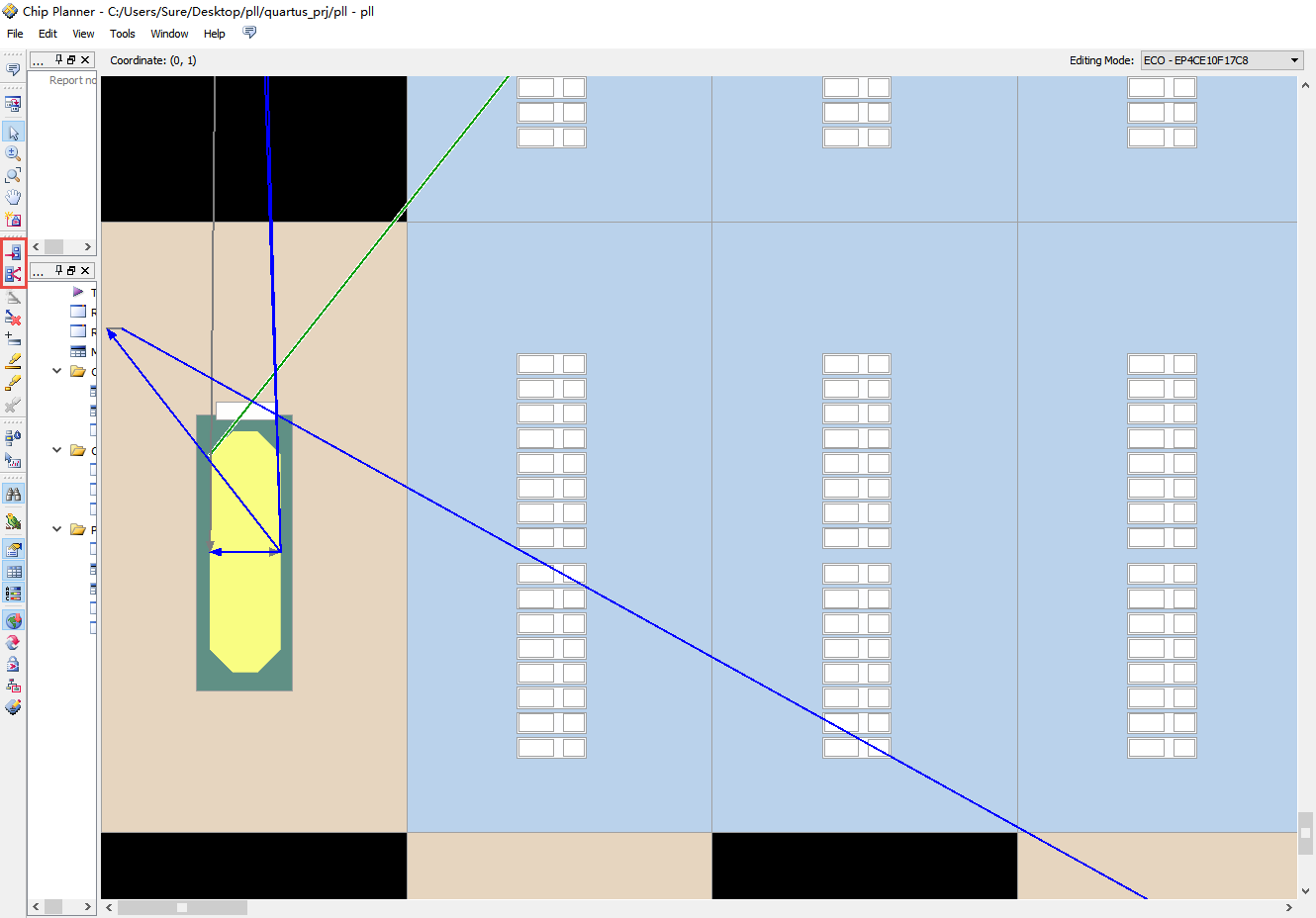

如圖5所示,選中該PLL後點擊左側的圖標顯示扇入扇出線路徑,可以看到PLL在晶片內的連接關係。

圖 5

如圖6所示,我們回到工程介面點擊「Assignment Editor」圖標來約束PLL的位置。

圖 6

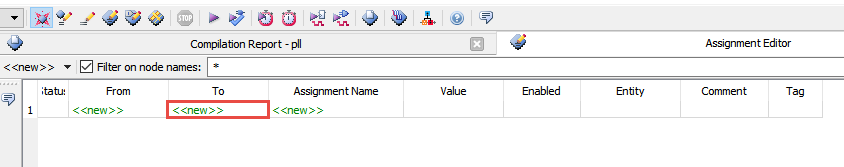

如圖7所示,在打開的「Assignment Editor」介面中點擊「To」下面的「<<new>>」添加要約束的項。

圖 7

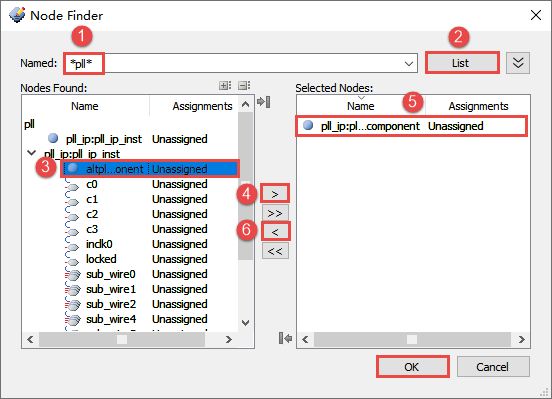

在打開的「Node Finder」介面中我們找到訊號的輸入key_in,如圖8所示,根據序號順序,在①處的「Named :」選項框中輸入「*pll*」,點擊 ②處的「List」,在③處的「Node Found :」列表中就會列出名為altpll:altpll_component的訊號,雙擊③處的altpll:altpll_component 訊號或點擊圖標④,altpll:altpll_component訊號就被添加到⑤處的「Selected Nodes:」中了。如果我們想取消⑤處選擇的訊號則在「Selected Nodes:」選中該訊號後點擊圖標⑥即可。設置完畢後點擊「OK」退出。

圖 8

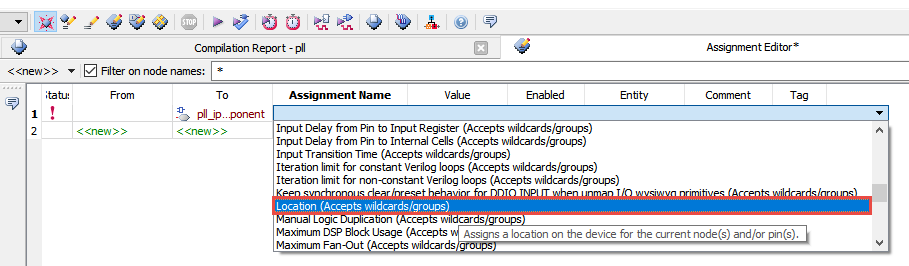

如圖9所示,設置「Assignment Name」,下拉列表找到「Location(Accepts wildcards/groups)」,這是設置位置的約束。

圖 9

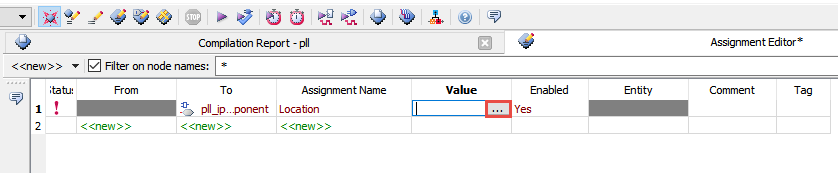

如圖10所示,點擊「Value」下的「…」。

圖 10

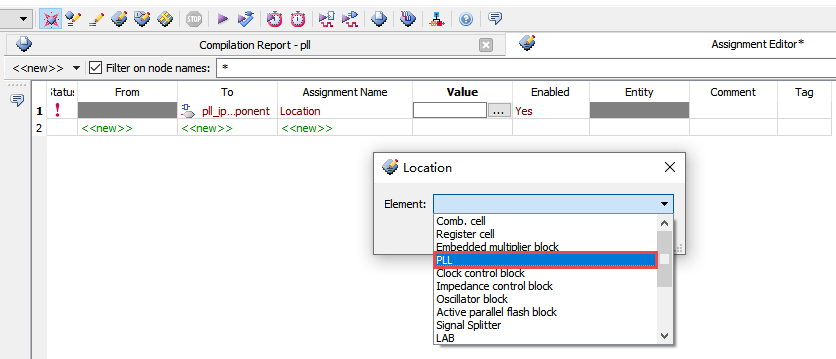

如圖11所示,在彈出的「Location」對話框中的「Element:」選擇「PLL」。可以看到在這裡我們還可以設置其他元素的位置。

圖 11

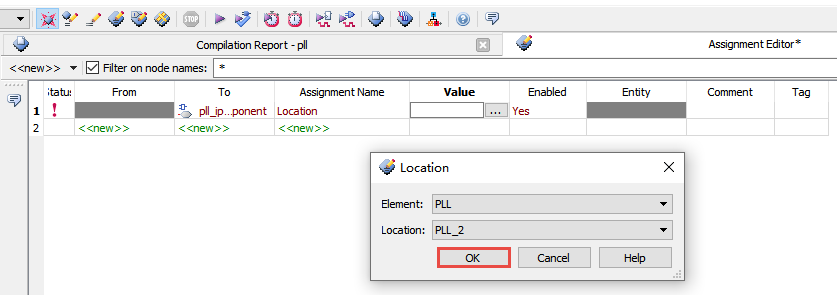

如圖12所示,「Location:」選擇「PLL_2」。

圖 12

如圖13所示,「Location」對話框設置完畢後點擊「OK」。

圖 13

全部設置完成後的結果如圖14所示。

圖 14

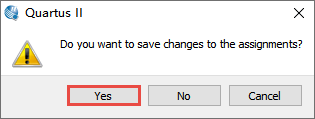

點擊「Start Compilation」圖標全編譯進行布局布線,否則無法重新映射資源。此時會彈出如所示的對話框,提示是否要保存更改,選擇「Yes」後會執行布局布線。

圖 15

當布局布線重新完成映射後我們再來看看Chip Planner視圖,如圖16所示,我們可以發現在版圖模型的右上角一塊顏色變深的區域,與左下顏色沒有變深的位置形成鮮明的對比,顏色變深的區域說明資源被佔用。

圖 16

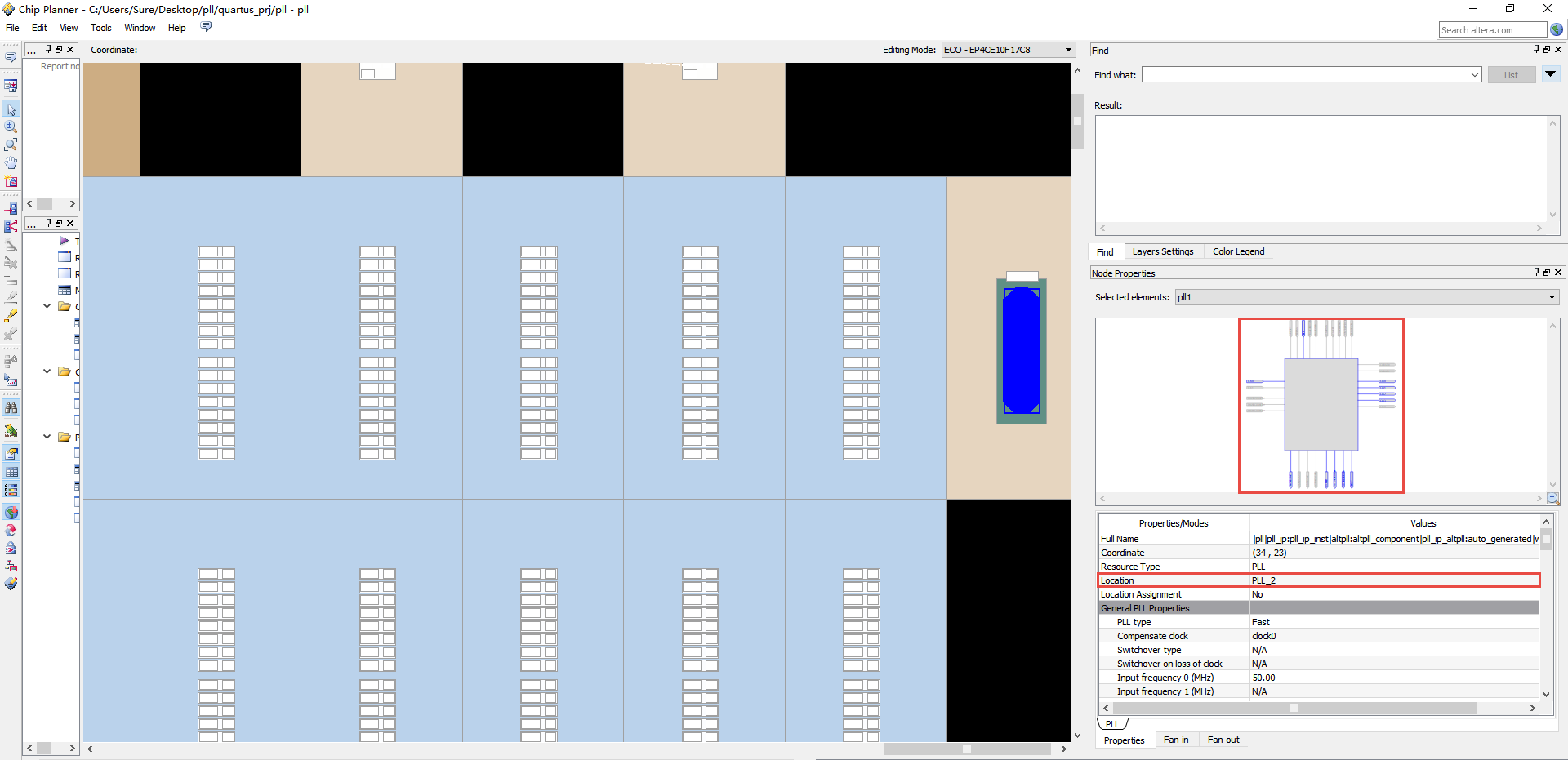

放大並點擊該PLL,如圖17所示,可以在右側看到該PLL的結構圖中顯示的部分藍色高亮訊號,下面「Location」則顯示了該PLL的名字為「PLL_2,說明已經成功映射上了。

圖 17

如圖18所示,選中該PLL後點擊左側的圖標顯示扇入扇出線路徑,可以看到PLL在晶片內的連接關係。

圖 18

修改PLL的映射位置意義何在呢?當我們的時序在某些情況下不好的時候就可以通過修改PLL的映射位置來調整時序,以實現時序的收斂。

歡迎加入FPGA技術學習交流群,本群致力於為廣大FPGAer提供良好的學習交流環境,不定期提供各種本行業相關資料!QQ交流群號:450843130