部分可重配置(PR)都成生成哪些.bit文件

- 2020 年 3 月 12 日

- 笔记

FullConfiguration Bitstreams

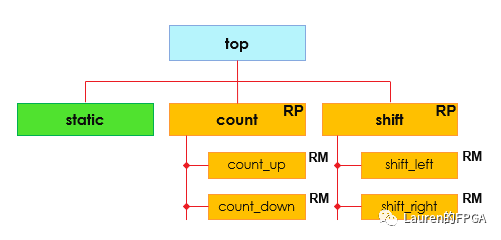

对于上图所示设计,不难判断会有两种configuration组合:

static+count_up+shift_left

static+count_down+shift_right

其余两种组合

static+count_down+shift_left

static+count_up+shift_right

可由前两种组合变换而来,只需要将其中的count RP对应的bit文件替换为count_down的bit文件或shift RP对应的bit文件替换为shift_right的bit文件即可。在设计评估阶段,通常会选择每个RP下时序较难收敛的RM与static组合,构成top,按照传统流程(非PR),检查设计中的关键路径,观察设计能否时序收敛。非PR流程和PR流程都会生成针对整个设计的bit文件,两者的格式、结构均一致。对于上述设计,会生成两个Full Configuration Bitstreams:

config1_count_up_shift_left.bit

config2_count_down_shift_up.bit

PartialBitstreams

对于每个RM,PR流程都会生成相应的bit文件,称之为Partial Bitstreams。通常,Partial Bitstreams的大小与RP对应的区域(每个RP的Pblock)成正比。例如,RP区域为整个FPGA资源的20%,那么相应的Partial Bitstreams的大小大约为Full Configuration Bitstreams的20%。针对上述设计,会生成以下Partial Bistreams:

不难看出,其命名也很有规律:full bitstream名+RP对应的Pblock名。

BlankingBitstreams

不同于full configuration bitstreams和partial bitstreams,Blanking bitstreams并不会由工具自动生成。生成Blanking bitstreams时,需要将RM设置为greybox。这里greybox并不是空设计,而是将RM的输入输出管脚连接到LUT。对于Vivado 2016.1之前的版本,如果目标芯片为7系列或Zynq,Blanking Bitstreams是建议生成的,其功能类似于后续要介绍的Clearing Bitstreams。从Vivado 2016.1版本开始,该Bitstreams不再需要。

ClearingBitstreams

不同于上述Bitstreams,Clearing Bitstreams只针对UltraScale系列芯片(不包括UltraScale Plus)。UltraScale系列芯片的结构决定了在加载新的RM对应的bit文件时需要先做清除工作,可以简单地理解为删除当前RP区域的逻辑(实际上并不是如此,而是关掉了该区域的时钟)。需要明确一点的是Clearing Bitstreams并不是Partial Bitstreams,其大小通常小于Partial Bitstreams的10%。同时,在切换Partial Bitstreams时一定要用到Clearing Bitstreams。例如count RP下的两个RM,count_up和count_down。当前的Partial Bitstreams为count_up,如果需要切换到count_down,就需要先加载count_up_clear.bit,再加载count_down.bit。

综上所述,PR流程可能会产生四类.bit文件:

Full Configuration Bitstreams

Partial Bitstreams

Blanking Bitstreams

Clearing Bitstreams(只针对UltraScale系列芯片)

针对上图所示设计,如果目标芯片为UltraScale系列芯片,其生成的bit文件如下图所示。