AXI MCDMA 仿真與工作流程分析

- 2022 年 9 月 8 日

- 筆記

- Verilog IP

說明

關於背景知識,可以先看 //www.cnblogs.com/xingce/p/16386108.html

引用一段官方的說明,AXI MCDMA存在的主要目的是為了節約資源,我們想要使用這個模塊的主要目的也是為了降低資源消耗,從而可以將系統部署在更小面積的FPGA芯片上,當然,具體的效果還需要進一步的測試,先對該IP做一些仿真和在線測試吧。

FPGAs have been providing DMA engines in the Programmable Logic for many years. To add to the existing DMA offering, Xilinx added a Multichannel DMA IP into the Xilinx IP Catalog to provide additional channels. Additional DMA channels provide a hardware segregation of data that ultimately provides more efficient management of data streams. This leads to an overall savings of Programmable Logic, while maintaining data movement throughput.

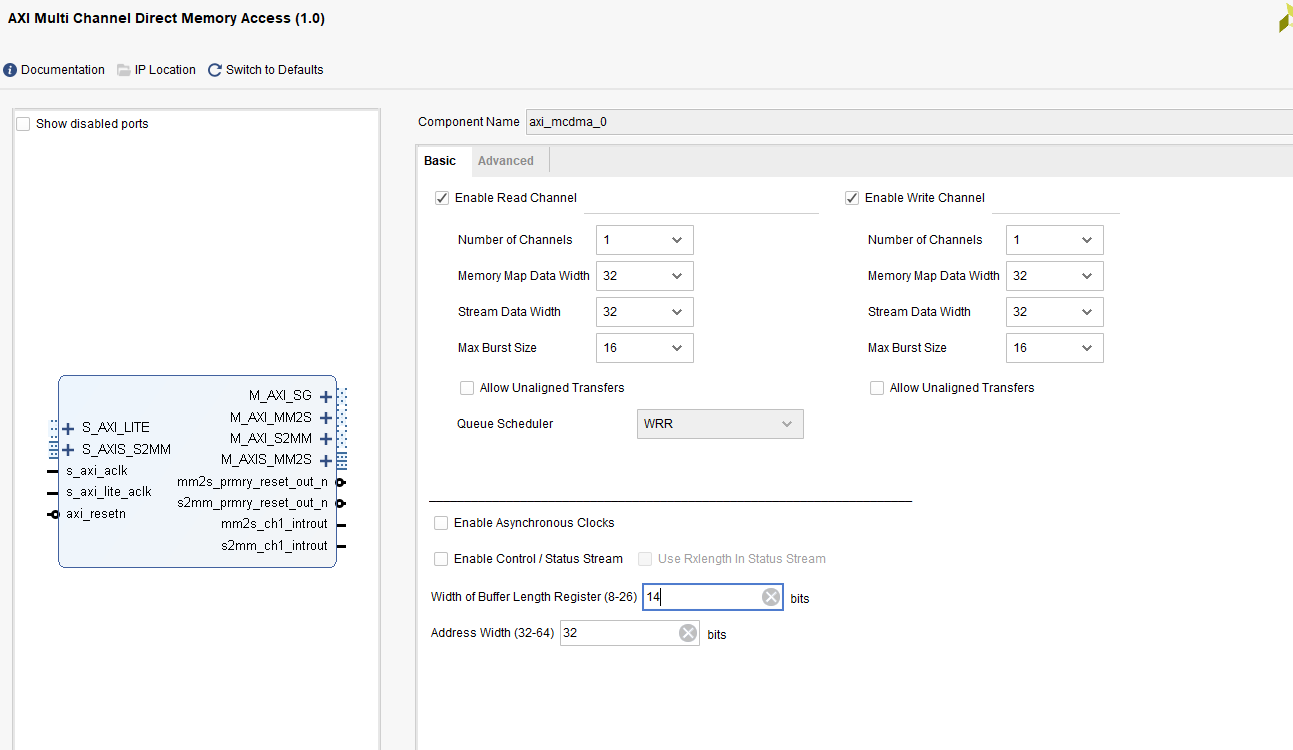

下圖是IP的接口和配置界面,更詳細的描述請移步官方手冊 //docs.xilinx.com/v/u/en-US/pg288-axi-mcdma

初步目標

在開始之前,先確定一個目標,我們希望通過該仿真的學習,搞清楚IP的基本配置、工作流程,然後去創建自己的仿真工程

官方仿真範例

選擇打開IP的example design,查看其仿真工程

先來看看頂層的*tb.v 仿真文件,裏面生成了1個200M的基準時鐘,然後發送了start開始信號,並檢測結束done信號與status信號,根據status的狀態輸出測試結論,核心的測試代碼不在這個文件裏面

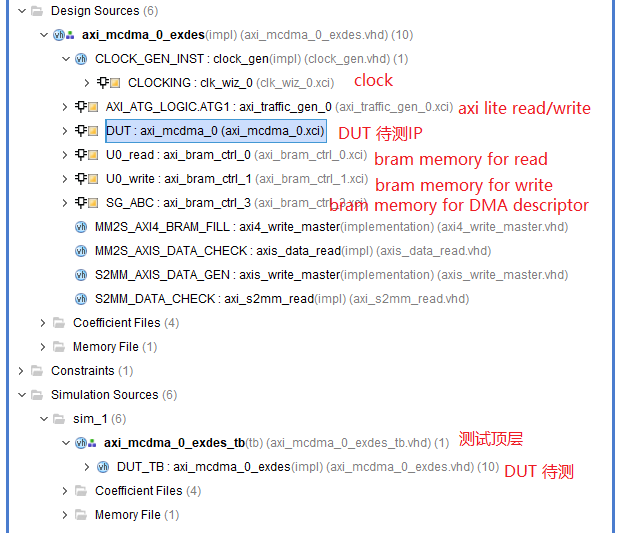

再來直接看DUT的頂層文件,先搞清楚對應的額層級關係

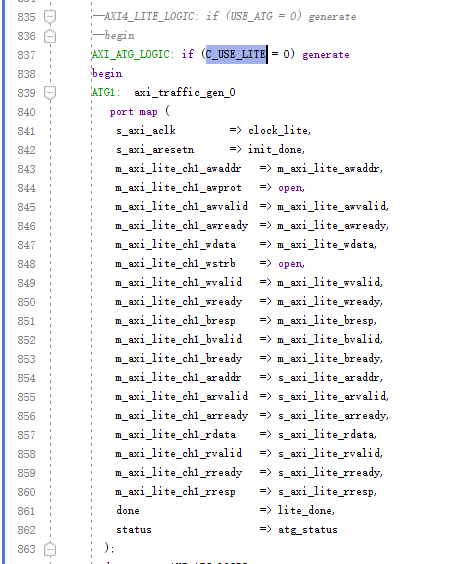

下圖表明axi_traffic_gen_0 用作mcdma的axi lite master模塊,完成對mcdma 寄存器的配置

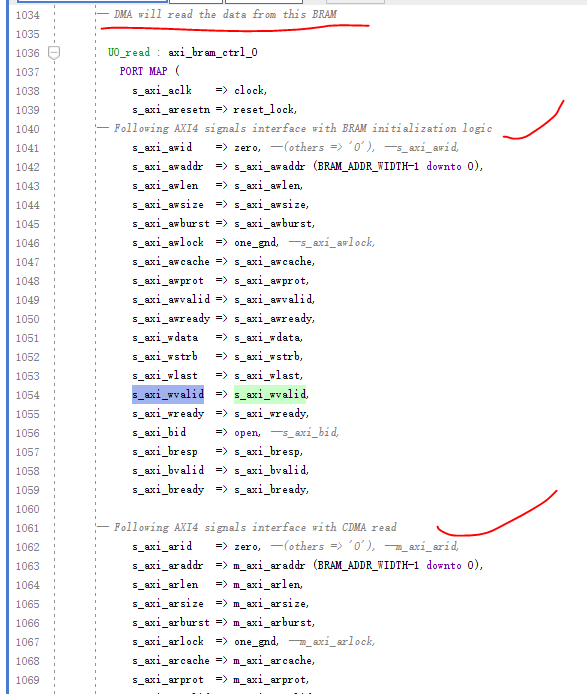

AXI MCDMA會讀出BRAM_CTL_0 中的數據,那麼BRAM 0中的數據怎麼才知道是不是對的,又需要一個模塊寫入測試數據,這個測試數據由axi4_write_master.vhd模塊完成,在系統複位解除後,就開始寫入測試數據

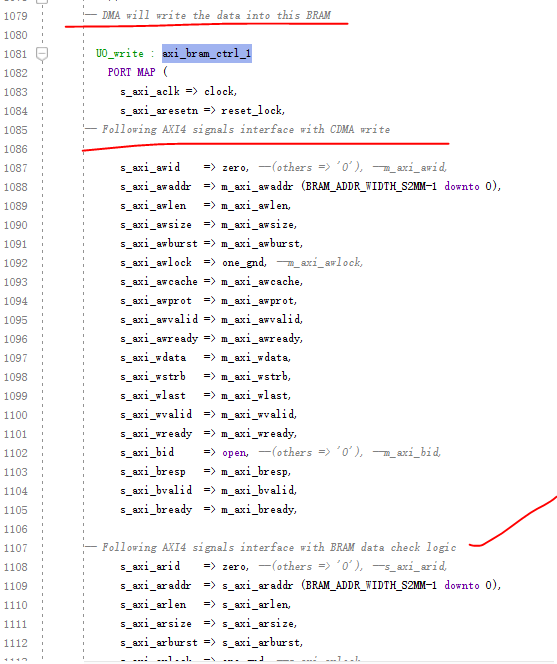

與讀出通道對應,AXI MCDMA會向BRAM_CTL_1寫入測試數據,檢查數據正確性的時候,測試邏輯是直接檢查的寫入信號,並不是將BRAM 1中寫入的數據讀出做校驗,這一點需要查看仿真波形,有可能設計人員偷懶,所以這樣寫的

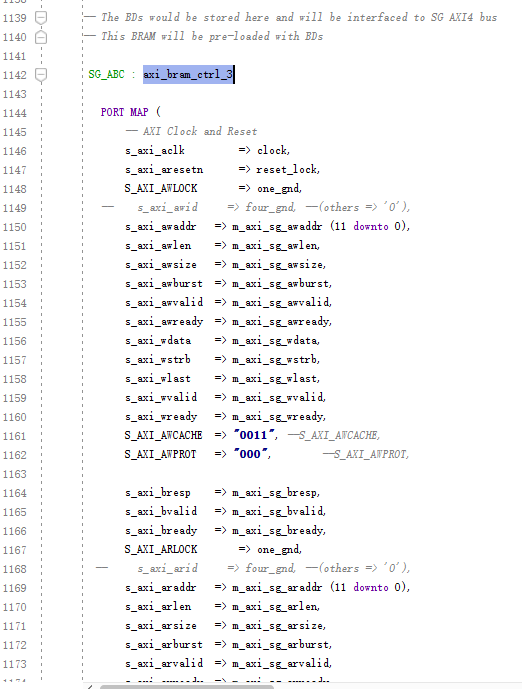

descriptor信息預先存儲在BRAM_CTL_3中,由AXI MCDMA的AXI SG接口將對應的信息讀出,對應的descripto信息存儲在”sg_mem.mem” 文件中

從以上信息基本可以看清整個仿真邏輯了,接下來再結合仿真信號看看真實的工作流程。

仿真信號查看

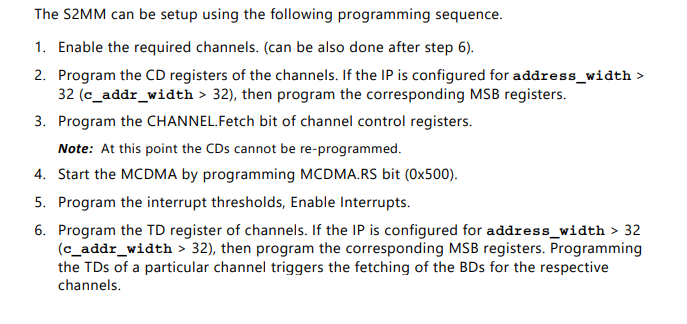

首先,根據IP手冊,AXI MCDMA開始工作之前,需要配置對應寄存器

先看S2MM 寫操作對應的流程,MM2S也是對應的流程,這裡不介紹了,可以看仿真的時序和IP手冊的說明

這是IP手冊建議的流程

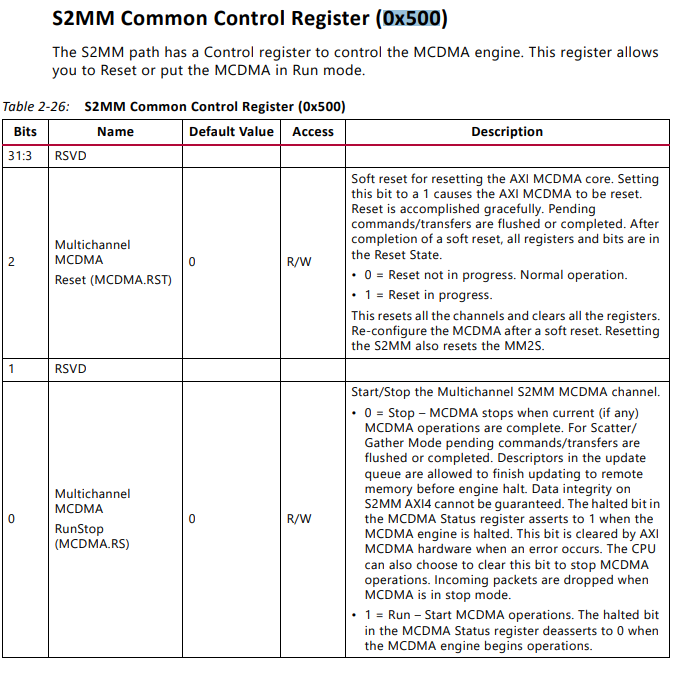

首先,需要先將MCDMA的S2MM 對應channels Run起來

向0x500 寄存器寫入控制數據

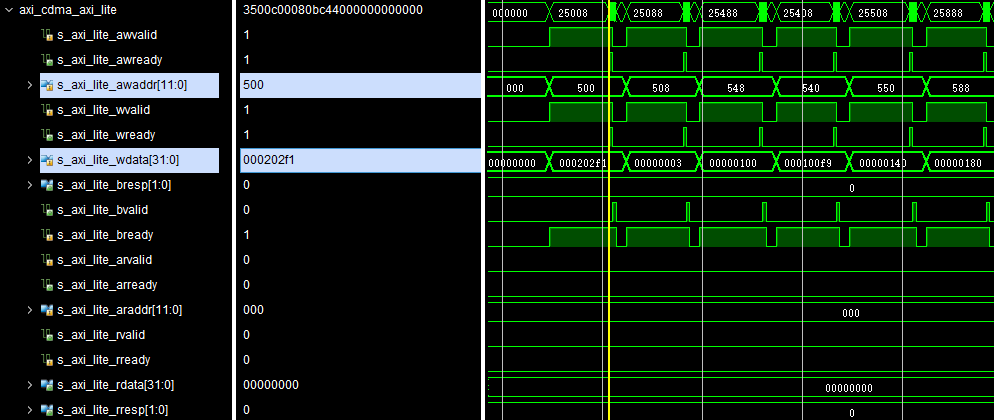

對應仿真時序圖如下,其中基地址為0x500 ,寫入數據為0x000202f1

使能對應通道

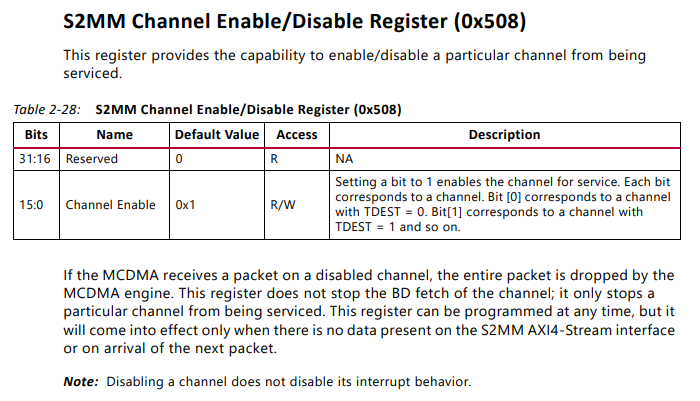

向0x508寄存器寫入對應參數,當disable的時候,並非真的stop了,而是當descriptor 鏈表對應也執行到含EOF標誌的鏈表時才真正停止。

(這裡有個問題就需要注意,如果是讀出操作,我們丟棄不需要的數據,如果是寫入操作,如何結束呢?)

應該向0x008寫入0x1 使能MM2S的channel 0,仿真實際寫入的是0x3,這個是由於仿真代碼是設定的2個通道,2個通道是合理的,因為只有這樣才能體現出Multichannel DMA的意義

配置descriptor 對應的地址

IP根據配置的descriptor地址去memory中fetch對應的descriptor鏈表,然後執行對應的axi讀寫操作

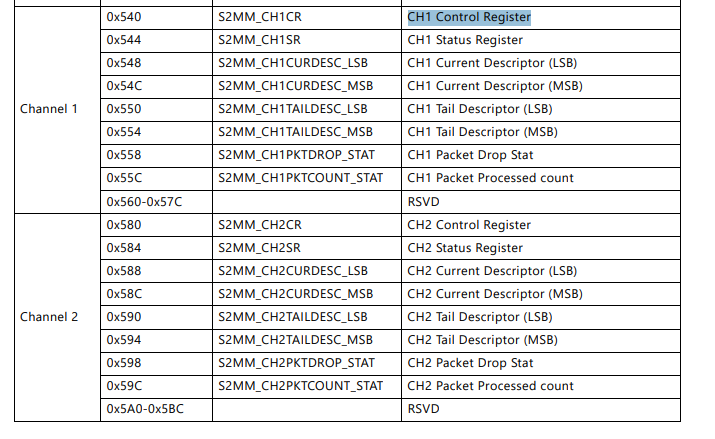

下面描述了對應channel 0 1的descriptor地址,由於我們是32bit 地址區間,所以只需要對應配置LSB 32bit地址即可,MSB 是在超過32bit地址空間的空間才有效

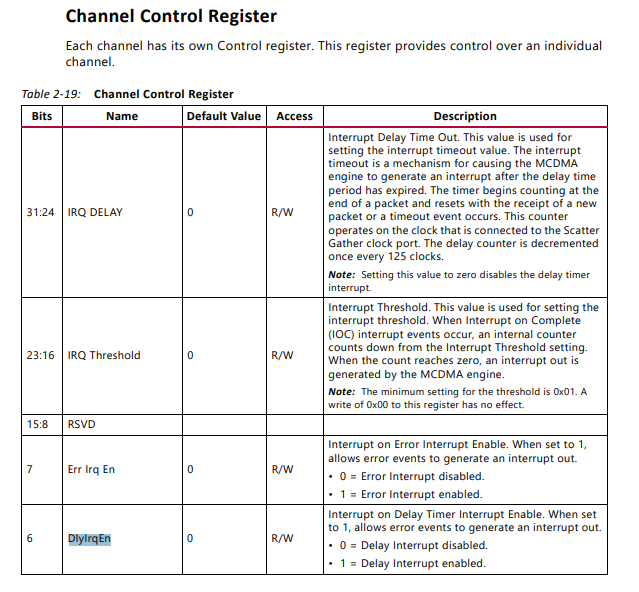

配置通道控制寄存器

每個通道都有自己的配置寄存器,這些寄存器第0個bit是開啟descriptor的featch,其它bit基本都是和中斷的產生相關的,仿真範例對S2MM和MM2S 通道進行了不同的設置,這個可以從仿真波形觀察得到

BD descriptor的讀取

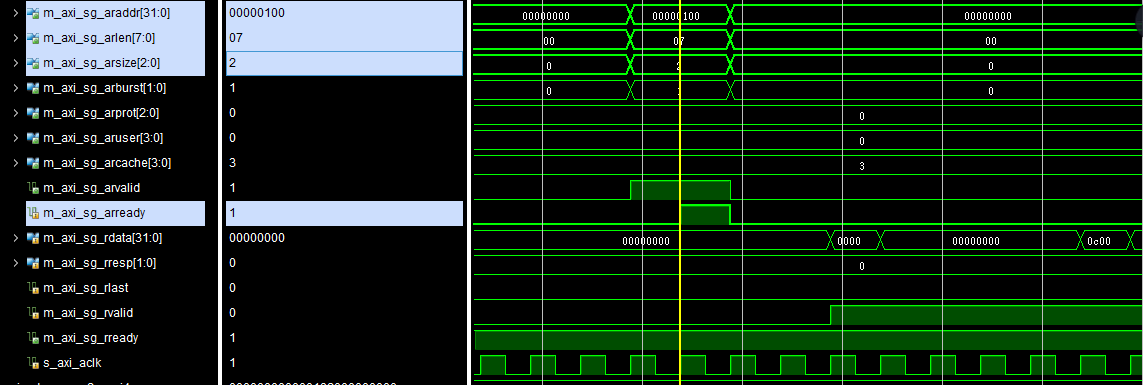

通過觀察寄存器寫入的值,可以看出S2MM 的channel 0 對應寫入的current BD 地址為0x100 , nexr BD 地址為0x140

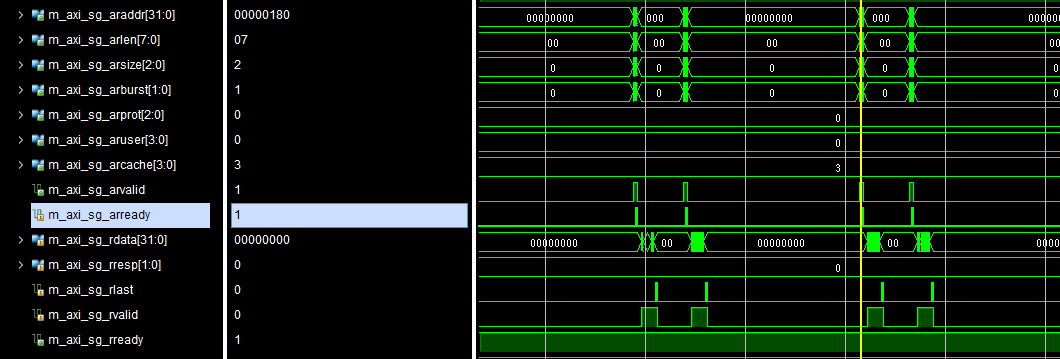

下圖是對應的時序,圖中不能看出具體的地址,如果想看的話可以自己仿真,然後放大觀察

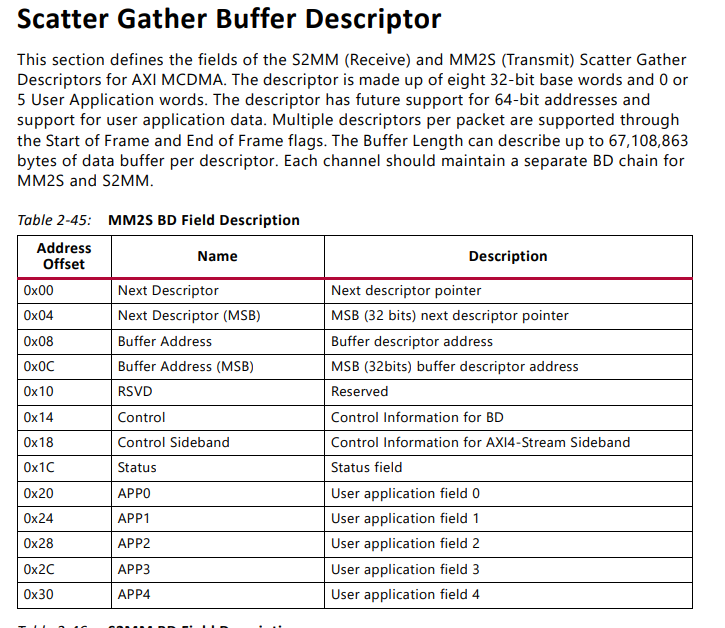

BD descriptor 描述,下圖描述了MM2S對應的descriptor描述,S2MM也是類似的內容,AXI MCDMA對應的通道會根據這個descriptor完成對應的dma操作

在這個仿真範例中,我們看一下

SG從0x100地址讀指定 8*32bit的descriptor數據,然後根據descriptor去讀取數據

整體看下來,這個仿真demo是非常簡易的,不能覆蓋真實的工況,下一步需要上機測試才能更好的模擬真實工作場景