探索ADC的原理(自製3位並行比較型ADC)

摘要

本文通過列舉歷史中出現的產品,梳理了模數轉換器在20世紀30年代~~20世紀80年代末的發展歷史。接下來,簡要介紹模數轉換器的原理、技術指標、分類和未來發展方向。最後,提供了一種自製3位FLASH型ADC的方法(該方法經過了作者的測試且價格在20元以下)。

參考文獻

涉及到的數據手冊(eyg7)

Flash ADC_Chapter 13 – Digital-Analog Conversion

《Analog-Digital Conversion》 Chapter I Walt Kester

ADC的歷史

世界上記載的第一個」純電子「的A/D轉換器於1939年被亞歷克·哈利·里夫斯(Alec Harley Reeves)發明,該設計的採樣率為6KSPS,分辨率為5位。

亞歷克·哈利·里夫斯設計的A/D轉換器原理圖,《Analog-Digital Conversion》 Chapter I Walt Kester

1947年,鍺晶體管于貝爾實驗室誕生。

1946年,ENIAC問世,現代數字計算機的鼻祖,為A/D的蓬勃發展做鋪墊。

1948年,貝爾實驗室發明了5位、8KSPS的逐次逼近型A/D轉換器。

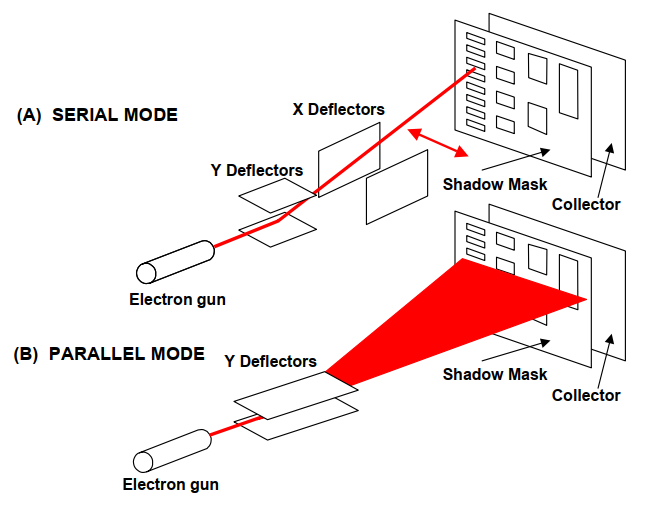

得力於電子束編碼管技術,在1960年左右出現了12MSPS、9位的編碼器(A/D)。

電子束編碼管原理圖,《Analog-Digital Conversion》 Chapter I Walt Kester

1954年,硅晶體管於德州儀器誕生。

1954年,伯納德·M·戈登(Bernard M. Gordon)發明了11位、50KSPS的基於真空管的A/D,這被認為是世界上第一個商業化的A/D轉換器。「Datrac」功率500W,售價8000~~9000美元。

伯納德·M·戈登發明的 「Datrac」,《Analog-Digital Conversion》 Chapter I Walt Kester

1958/1959,集成電路問世,德州儀器(1958),仙童半導體(1959)。

1963~1965年,為了給美國軍方的雷達提供高速A/D,貝爾實驗室的John M. Eubanks和Robert C. Bedingfield研發了8位、10MSPS的A/D,其功率為150W、售價10000美元。

John M. Eubanks和Robert C. Bedingfield研發的A/D,《Analog-Digital Conversion》 Chapter I Walt Kester

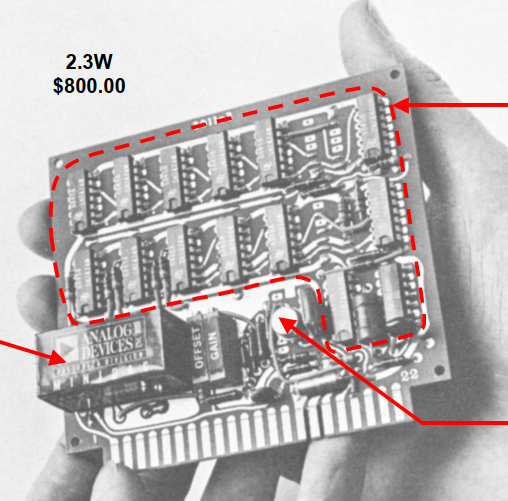

1969年,Pastoriza公司利用分立元件製造了12位、10us、2.3W的逐次逼近型A/D樣機—-“ADC-12U”,售價800美元。

“ADC-12U”原型機,《Analog-Digital Conversion》 Chapter I Walt Kester

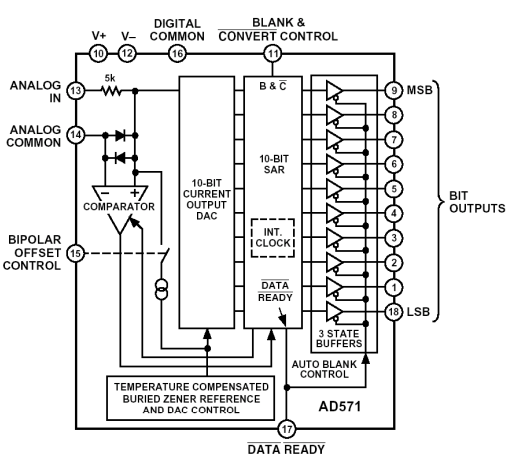

1978年,Paul Brokaw設計了第一個完整的單芯片ADC,型號為AD571,使用了雙極型工藝,參數為:10位、25us、SAR結構。同年,誕生了最具重要意義的SAR ADC–AD574。這時的A/D可以說開始走向現代。

AD571,源

AD571框圖,《Analog-Digital Conversion》 Chapter I Walt Kester

1988年,Crystal Semiconductor推出了世界上第一個單芯片商業化的ε-Δ ADC–CSZ5316,參數:16位、20KSPS,可以用於語音處理。

接下來的歷史中,各廠商不斷改進ADC的性能、推出更多不同用途的ADC。總而言之,就是讓ADC進入千家萬戶。

ADC的原理

ADC(Analog to Digital Converter)是一類將模擬信號(連續信號)轉換為數字信號(離散信號)的器件,按原理可分為:並行比較型A/D轉換器(FLASH ADC)、逐次比較型A/D轉換器(SAR ADC)和雙積分式A/D轉換器(Double Integral ADC)。

模擬信號,下圖中的ui(t)是一個輸入的模擬電壓信號,可以想像成從一個麥克風輸出的音頻信號。

數字信號,現代計算機能夠處理的信號,表現為下圖中的「n位數字量輸出」。

香農-奈奎斯特(Shannon & Nyquist)採樣定理規定,使恢復出的信號不失真的條件:採樣頻率大於原始信號頻率的兩倍,即 Fs >= 2Fi

一個連續的電壓信號ui(t)通過一個由方波CPs控制的開關S之後施加到電容C上,由於電容兩端的電壓不會突變,可知在S斷開時C將維持ui(t)在開關斷開瞬間的電壓一段時間,直到開關S再次打開。這樣,一個模擬的電壓信號就轉換成了採樣展寬信號us(t),其中CPs的頻率就是採樣頻率Fs。然後,由ADC的數字編碼電路將採樣展寬信號us(t)轉換成n位的數字量dn-1 : d0並輸出。

通過上述步驟,一個連續的電壓信號就轉換成了n位的數字量,而實現該過程的器件叫做模擬-數字轉換器(ADC)。

AD轉換的一般原理,“數字電子技術” SWPU

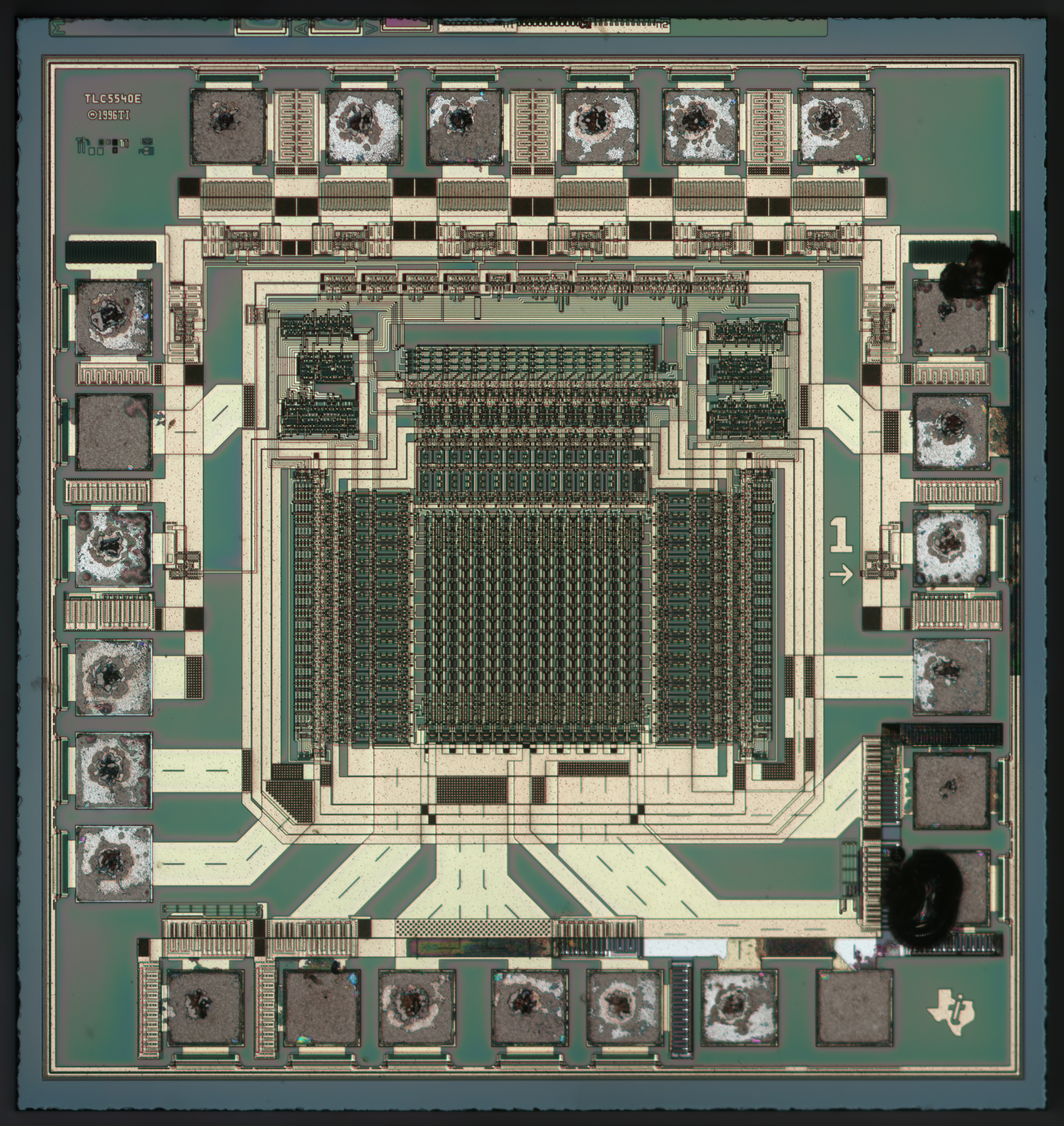

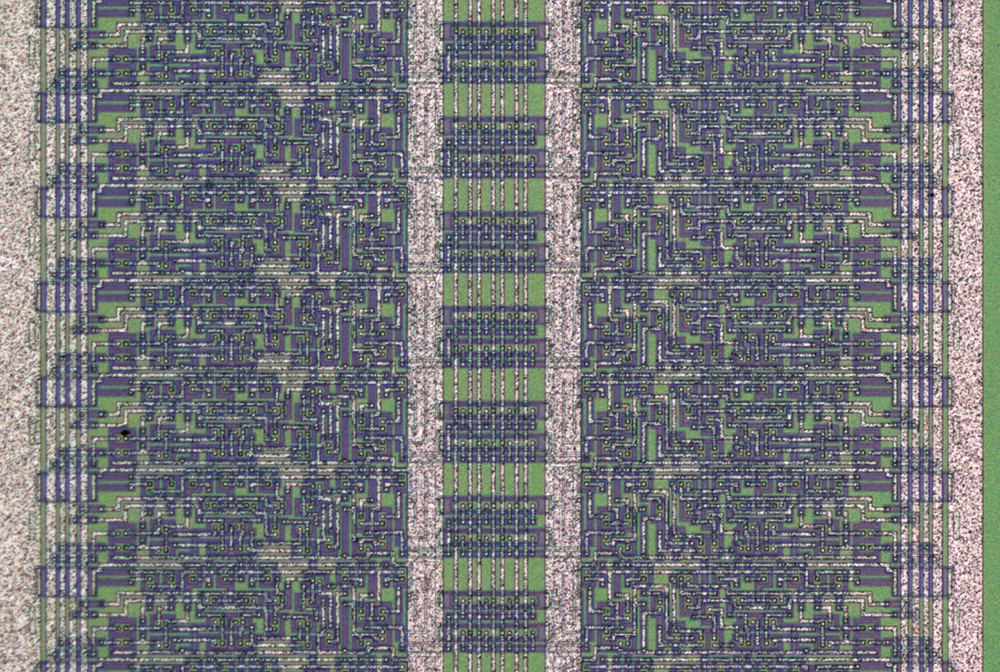

TLC5540I,8位、40MSPS、CMOS工藝的並行比較型A/D轉換器的版圖,//zeptobars.com/,license: CC BY 3.0,未修改

ADC的主要性能指標

分辨率:ADC能分辨的最小電壓,通常用位數表示,例如:8位。一個n=8位的ADC,參考電壓為5V,則其能分辨的最小電壓為 5 / 2^n = 19.53mV

轉換時間:ADC從控制信號到來開始,到輸出端得到穩定的數字信號所經歷的時間。

轉換精度:ADC輸出的數字量所表示的模擬值與實際輸入的模擬量之間的偏差。

ADC的分類

並行比較型A/D轉換器:這是本文嘗試構建的ADC,其由電阻分壓器、電壓比較器(運算放大器)、D觸發器和優先級編碼器構成。其原理簡單,將在後文介紹。

優點:1.轉換時間最短,其轉換周期為通過比較器、觸發器和優先級編碼器的時間總和(見下式),這個數值通常很小。

T轉 = T比 + T寄 + T編

缺點:1.造價高昂,隨着分辨位數的提高,所需的元件幾乎按幾何級數增長,如:一個n位的並行比較型ADC,需要2^n – 1個比較器和2^n – 1個觸發器,假如n=12,那麼一共需要8190個比較器和觸發器!

2.對集成電路的工藝要求很高。

常見的型號:AD9012,TTL工藝,分辨率為8位,採樣率為100MSPS,模擬輸入電壓範圍 -Vs~~+0.5V(Vs為芯片供電電壓)。

AD9002,ECL工藝(射極耦合邏輯),分辨率為8位,採樣率為150MSPS,模擬輸入電壓範圍 -Vs~~+0.5V(Vs為芯片供電電壓)。

AD9020,TTL工藝,分辨率為10位,採樣率為60MSPS,雙極性模擬輸入(+-1.75V)。

3位並行比較型A/D轉換器原理圖,《數字電子技術》第六版 康華光

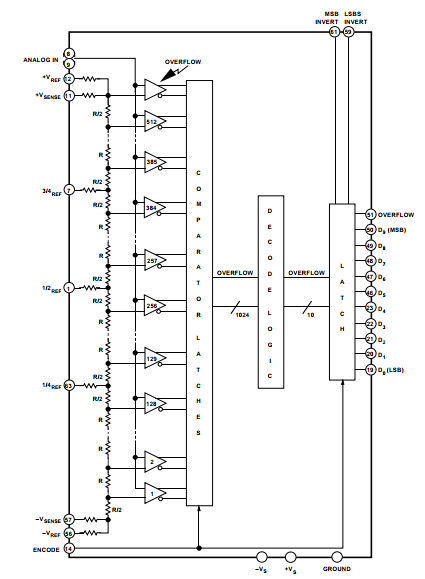

AD9012原理圖,Analog Devices

AD9002原理圖,Analog Devices

AD9020原理圖,Analog Devices

1107PV2,蘇聯,8位、20MSPS,典型的並行比較型A/D轉換器的版圖,//zeptobars.com/,license: CC BY 3.0,未修改

1107PV2,蘇聯,8位、20MSPS,典型的並行比較型A/D轉換器的比較器的版圖,//zeptobars.com/,license: CC BY 3.0,未修改

逐次比較型A/D轉換器:原理像天平,對輸入的模擬電壓信號與不同權值的電壓做多次比較,使得轉換所得的數字量在數值上不斷逼近輸入的模擬量。通常由控制邏輯電路、數據寄存器、移位寄存器、D/A轉換器(Digital Analog Converter)和電壓比較器構成。

優點:1.轉換速度快。其轉換周期等於 分辨率 * 時鐘周期(見下式),如一個8位的逐次比較型A/D轉換器,時鐘周期為10us,則其轉換周期為80us。

T轉 = n * Tclk (n為分辨率)

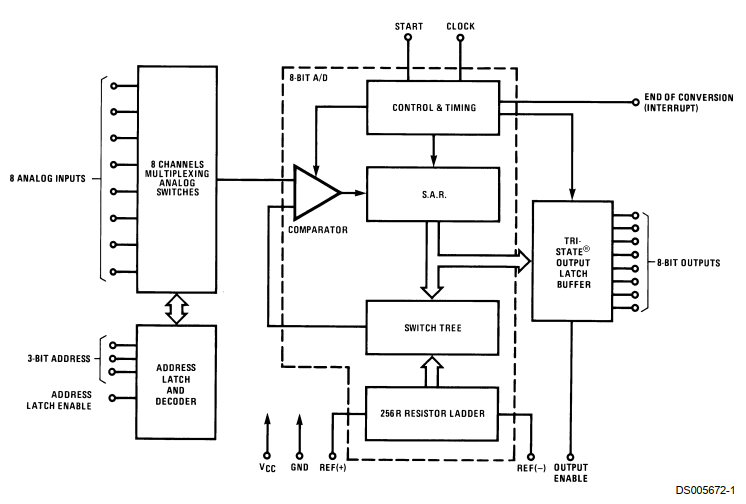

常見的型號:1.ADC0808/ADC0809,8位逐次比較型A/D轉換器,轉換時間100us,輸入電壓範圍0~~5V,可接入8個模擬量輸入。

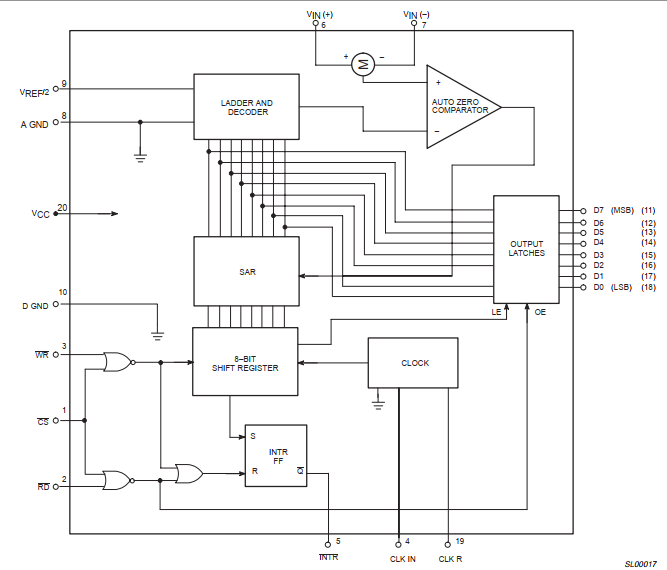

2.ADC0803/ADC0804,8位逐次比較型A/D轉換器,在1MHz的時鐘頻率下,轉換時間在66~~73us之間,支持一對差分模擬電壓輸入。

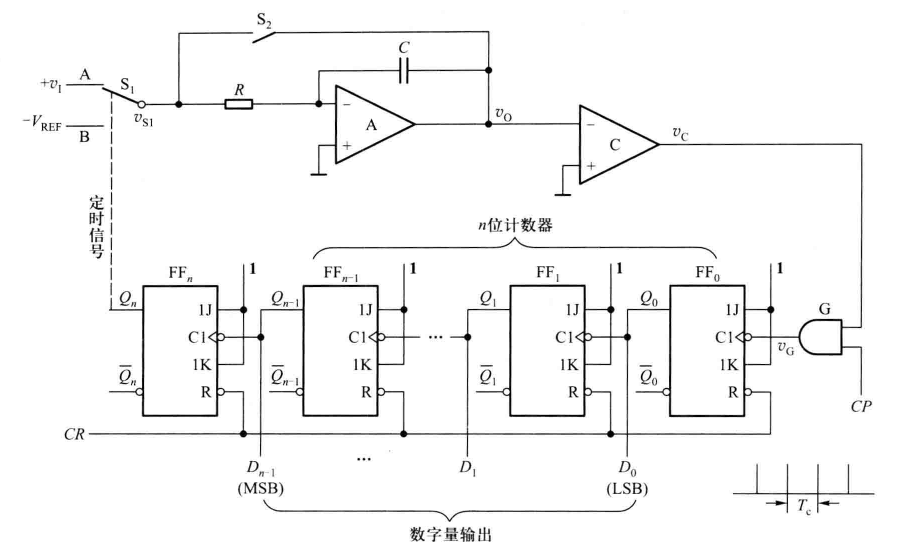

逐次比較型A/D轉換器原理圖 ,《數字電子技術》第六版 康華光

ADC0808/ADC0809原理圖,National Semiconductor

ADC0803/ADC0804原理圖,Philips Semiconductors

雙積分式A/D轉換器:一種間接的A/D轉換器,其分別對輸入電壓和參考電壓進行兩次積分,將輸入電壓平均值變換成與之成正比的時間間隔,然後利用時鐘脈衝和計數器測出此時間間隔,進而在輸出端得到與模擬量相應的數字量。通常由積分器(運算放大器及相應的外部電路)、過零比較器(運算放大器)、時鐘脈衝控制門和計數器等構成。

優點:1.抗工頻干擾能力強。通過對輸入電壓的平均值進行變換來實現抗干擾。

缺點:1.轉換速度最慢。

常見的型號:TLC7135,4.5位雙積分式A/D轉換器,CMOS工藝,差分電壓輸入。

雙積分式A/D轉換器原理圖,《數字電子技術》第六版 康華光

TLC7135數字部分原理圖,Texas Instruments

ADC的未來發展方向

ADC在未來會變得性能更強、價格更低、功耗更低、通用性和專業性更強。

性能:從歷史上看,對ADC性能的改進主要集中在改進架構和改善製造工藝兩個方面。ADC有很多架構,典型的包括:FLASH、SAR和雙積分;其他的有:流水線等。在集成電路發展的過程中,出現了許多的工藝:雙極性、ECL、CMOS、CB、BiCMOS、GaAs……這些工藝可以幫助改進ADC的性能。

價格:隨着集成電路工藝的不斷成熟,價格變低只是時間問題。

功耗:得力於集成電路工藝的改善,如:使用更低線寬的IC的功耗會低於高線寬的IC。功耗同時也取決於ADC架構。

元件清單(」 * 「為可選)

————————————————————時鐘發生器部分——————————————————————–

NE555 *1

*DIP-8芯片座 *1

8位撥碼開關 *1

*3pin排針 *1

3.9K電阻 *1

68K電阻 *1

10uF無極電容 *1

1uF無極電容 *1

100nF無極電容 *1

10nF無極電容 *2

1nF無極電容 *1

100pF無極電容 *1

10pF無極電容 *1

1pF無極電容 *1

所有元件合照(時鐘發生器部分)

———————————————————————————————————————————————–

————————————————————數模轉換器部分——————————————————————–

MCP6004 *1

*DIP-14芯片座 *1

CD4042B *1

CD4532B *1

*DIP-16芯片座 *2

2K可調電阻器 *1

330R電阻 *3

390R電阻 *1

1K電阻 *5

LED-G *3

*Pin-3排母 *1

*Pin-2排針 *1

所有元件合照(數模轉換器部分,不含Pin-2排針)

———————————————————————————————————————————————–

電路原理

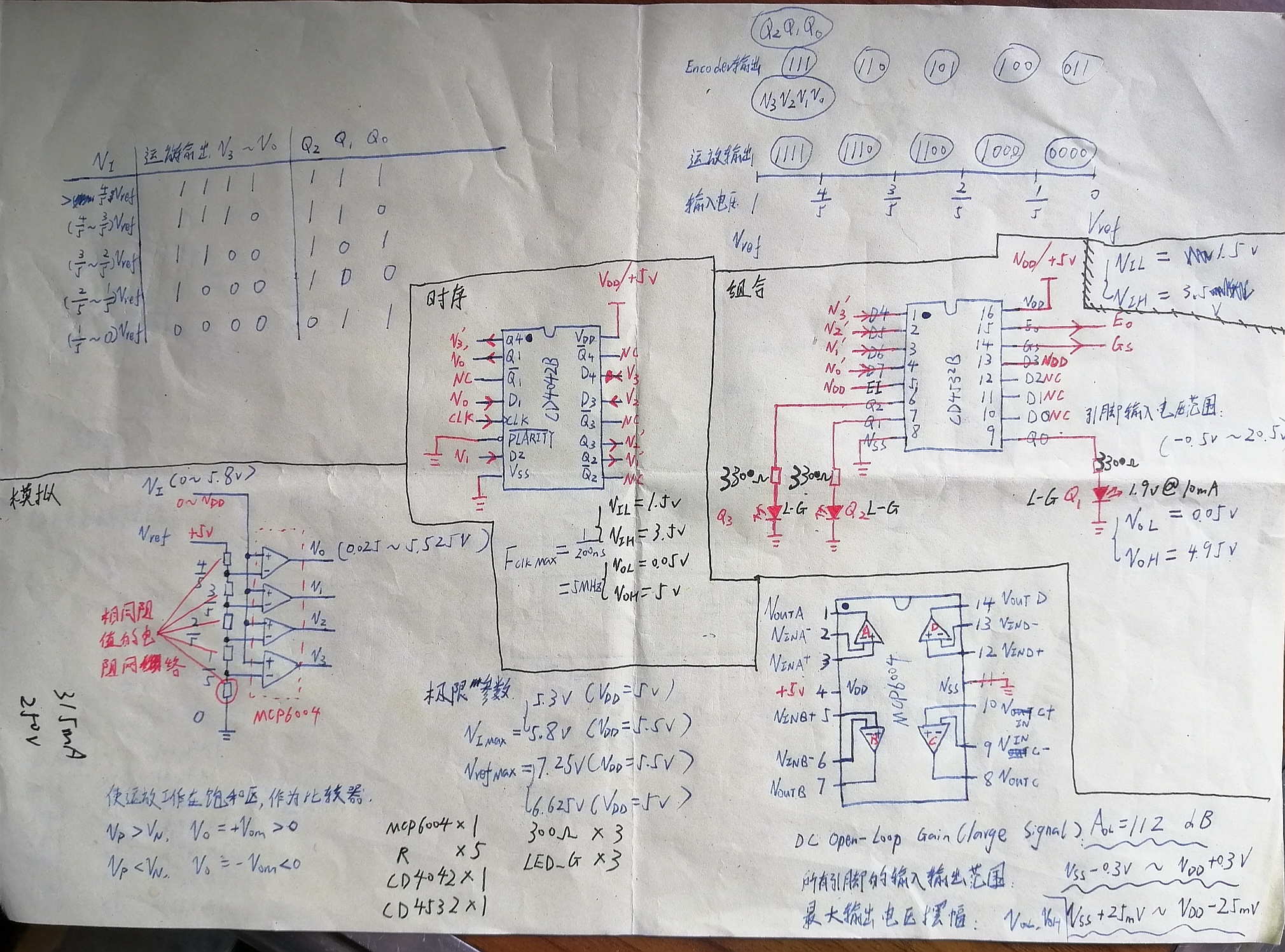

總原理圖(1)

總原理圖(2)

————————————————————時鐘發生器部分——————————————————————–

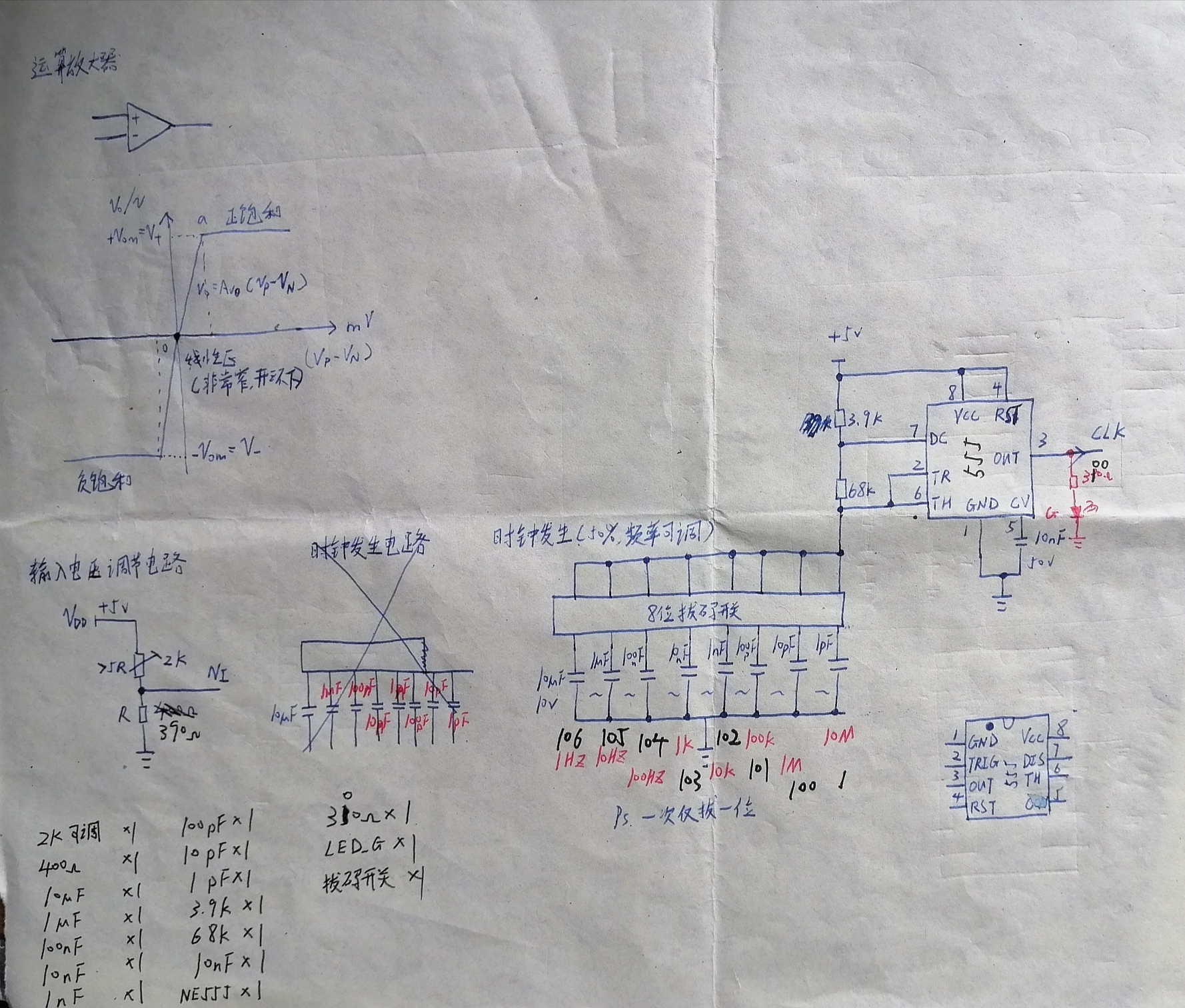

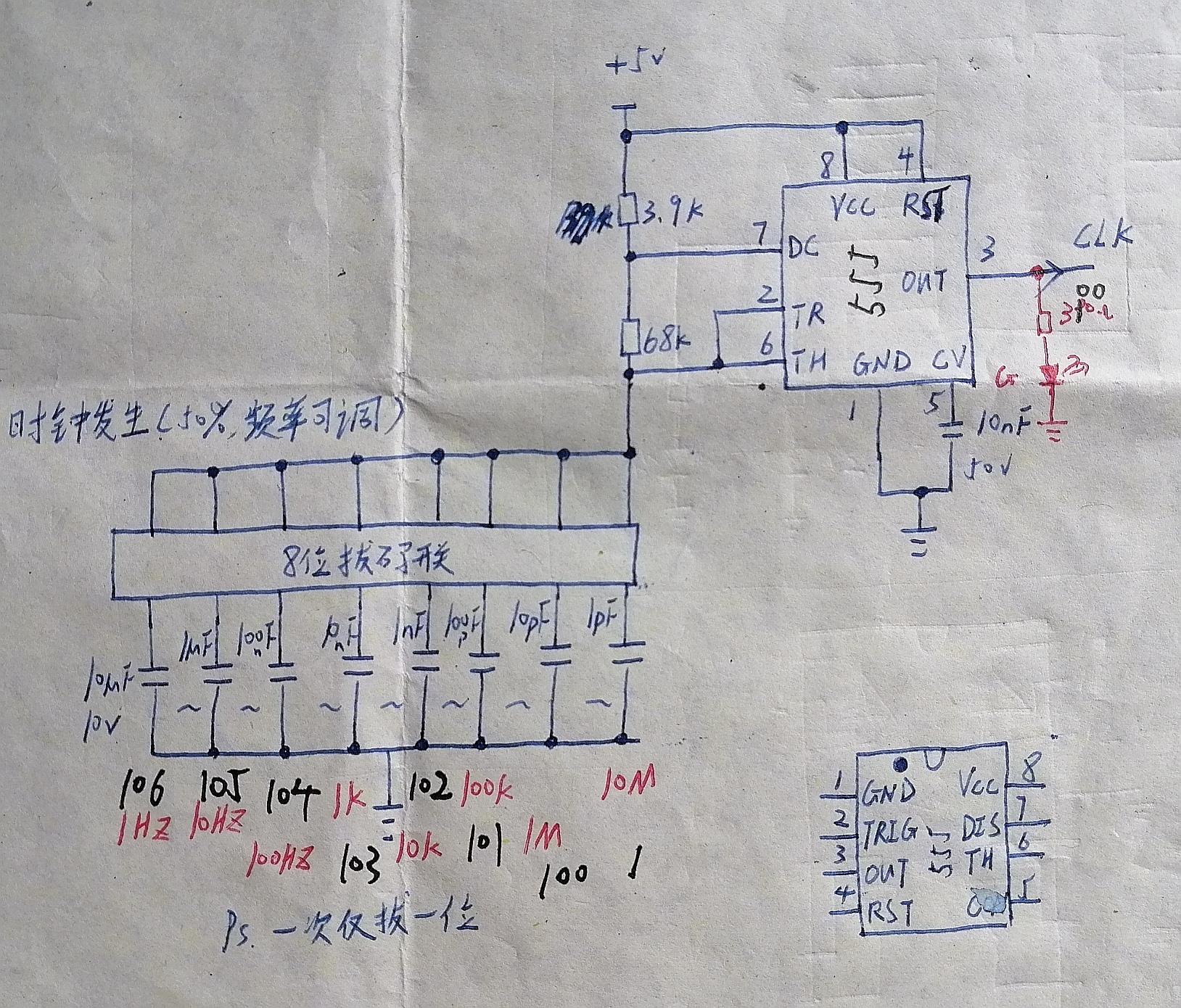

555定時器工作在多諧振蕩器模式,通過撥碼開關選擇不同的電容來產生不同頻率的方波。

基於555定時器的時鐘發生器原理圖

————————————————————————————————————————————————

————————————————————數模轉換器部分——————————————————————–

比較器:左側的電阻分壓網絡為右側的四個比較器的反相輸入端提供階梯狀的參考電壓(4V、3V、2V、1V),可調電阻模擬輸入到四個比較器同相端的模擬電壓(0~~5V)。比較器通過比較同相輸入端與反相輸入端電壓的大小,輸出0V(Vp<Vn)或5V(Vp>Vn)給後面的D鎖存器。

運放的特性圖

四路D鎖存器:在時鐘的每一個上升沿,將四個運放輸出的電壓(比較結果)存儲起來並交給後面的編碼器。

優先級編碼器:對來自鎖存器的四個比較結果進行編碼,並輸出給計算機處理(如果有計算機的話)。

———————————————————————————————————————————————–

集成電路簡介

MCP6004:微芯公司生產的低功耗1MHz帶寬的4路運算放大器,本項目的運算放大器均工作在飽和區。

MCP6004實物圖

MCP6004引腳定義

CD4042B:CMOS四路D鎖存器,在本項目中使用上升沿觸發,時鐘由555定時器提供,用於保存MCP6004輸出的4位數據。

CD4042B實物圖

CD4042B引腳定義

CD4042B真值表

CD4532B: CMOS的8位優先級編碼器,用於對CD4042B鎖存的數據進行編碼。

CD4532B實物圖

CD4532B引腳定義

CD4532B真值表

測試

————————————————————時鐘發生器部分——————————————————————–

此555時鐘發生電路,實際測試可以產生1Hz、10Hz、100Hz、1KHz、10KHz、100KHz、0.4MHz、0.7MHz的方波信號。實測中,產生的0.4MHz和0.7MHz與設計的1MHz、10MHz存在較大的誤差,可能是電容的問題(這兩個頻率對應所使用的是貼片電容)。

時鐘發生器(正面)

時鐘發生器(反面)

實測產生的最大頻率的波形(Vcc=5V下,Vpp=4.7V)

————————————————————————————————————————————————

————————————————————數模轉換器部分——————————————————————–

在時鐘為400KHz下,此並行比較型A/D可以正常工作;使用700KHz的時鐘會導致轉換故障。

主要參數:A/D分辨率為3位(嚴格來說只有2位,可以在不改變架構的情況下通過增加4個比較器拓增至3位)

採樣率為400KSPS~~700KSPS。

功耗:20mA@5V = 100mW (包含時鐘發生器部分)

當輸入電壓為2.5V時,輸出的情況(可以看出LED指示「101」,正好是對「1100」編碼的結果)

正面(1)

正面(2)

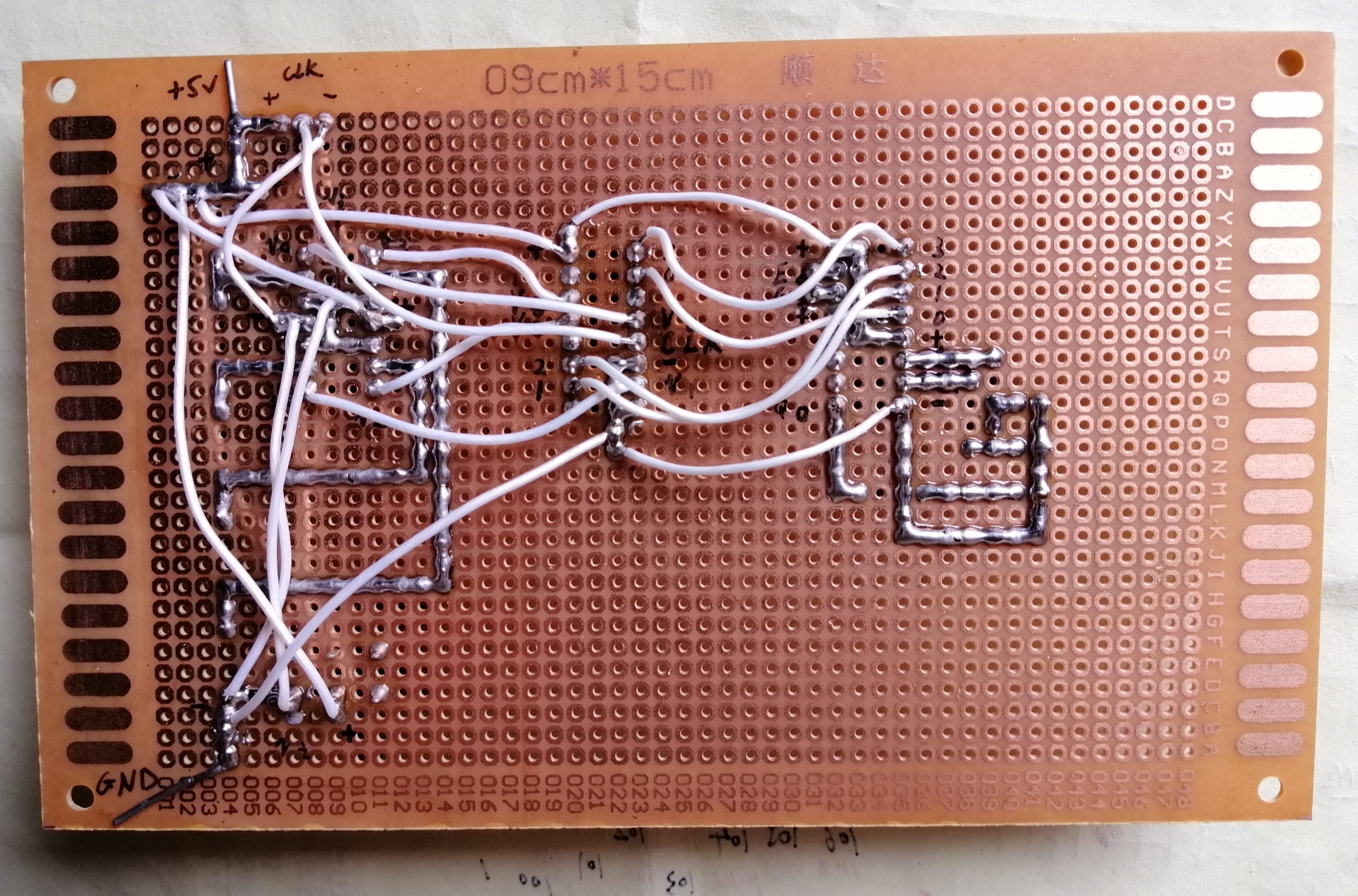

反面

———————————————————————————————————————————————–

聲明

此教程未經DLHC允許,禁止轉載。所有引用均註明了出處。DLHC保留所有權利。

由於本人學識有限且整理較為倉促,如有錯誤或不妥,請指正。