如何确定FPGA电路中DDR4的Speed bin 是否兼容?

- 2019 年 10 月 3 日

- 筆記

原创 by DeeZeng [ Intel FPGA笔记 ]

实际工作中,经常会碰到因为DDR3/4 或其他料件换料了,需要判断FPGA工程中IP设置需要重新改动,或是兼容直接换料就可行。

我个人倾向用 跑的速度的 speed bin 去设定,然后确认speed bin 是兼容的。

比如 DDR4 将换成2666 的chip, 但Arria 10 工程 只跑2133 或2400 的速度, 那我就按照2133 或 2400 的 speed bin 来设置。

但会需要确认 2133 、2400 speed bin 是被 2666 的chip 向下兼容的。

怎样查看Speed Bin 是否兼容呢?

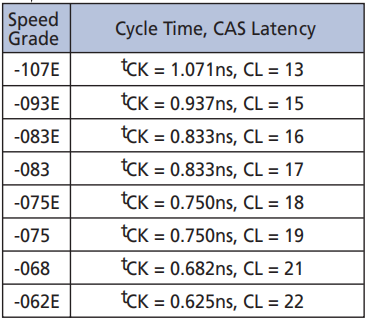

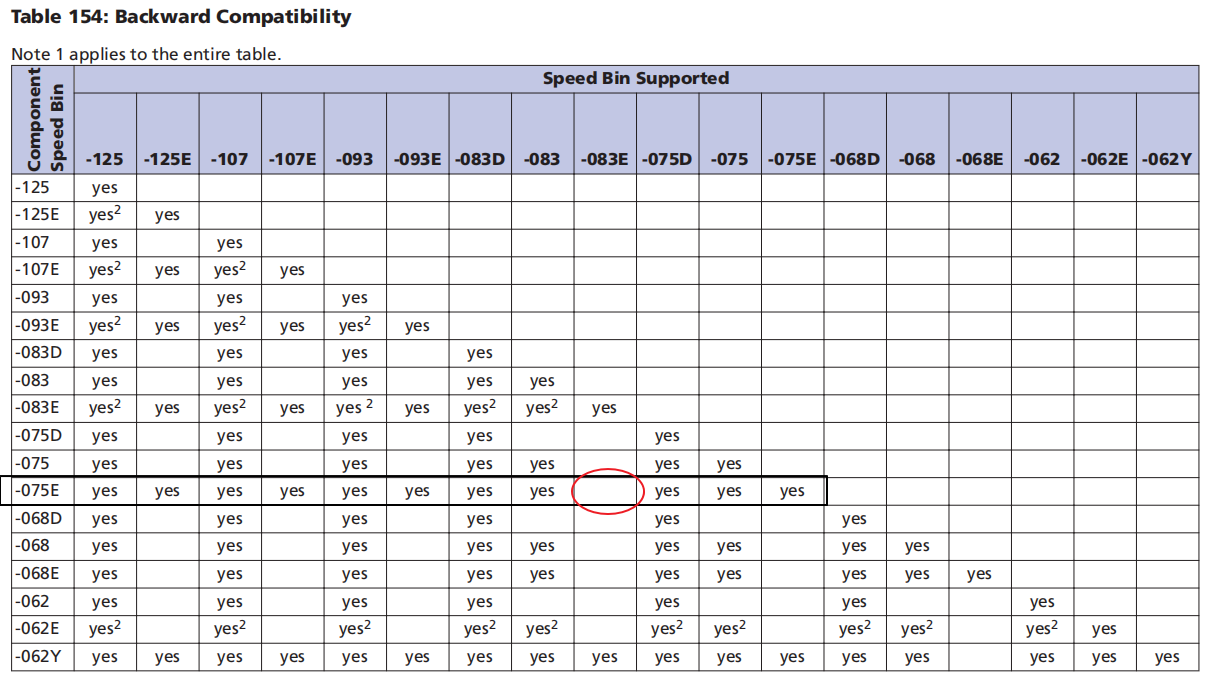

很简单, DDR4的datasheet中就有提,比如 Micron的这颗(随便找的一颗)

比如 我们选定 2666 的 component speed bin 是 075E。 那考虑兼容的时候 就会看到 不兼容 2400的 083E

这样设定IP的时候 我们就可以设定 2133 的093 或 093E speed bin 或 2400的 083 speed bin,而2400的083E speed bin 是不行的。

为什么会这样呢? 那有些参数是随 clock rate 变化的比如多少UI 是没影响。 但tRCD,tRP则是另外的情况,当然我们直接看兼容表就行了。

从兼容表也可以看出,并不是速度快就能直接替代速度慢的,有些参数还是不行的。 选替代料的时候需要注意一下。

是不是很简单,查看一下兼容表确认下就好!

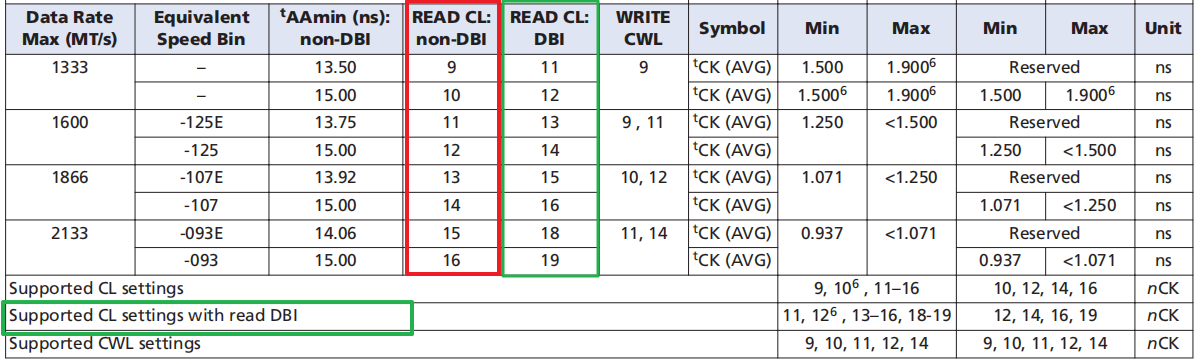

题外话:Data Bus Inversion(DBI) 这个功能可以在IP 中使能与否。

打开它可以让DQ IO 翻转更少,降低功耗。但它同时会增加latency(毕竟要多出一些判断来确定DQ 如何翻转)

可以在 Speed Bin 中看到:

所以打开DBI 与否 对 CL 的设定是有影响的。