包含多个矩形的Pblock

- 2019 年 10 月 30 日

- 筆記

pblock是否可以嵌套

Pblock是可以嵌套的,尽管这种应用方式并不常见。嵌套Pblock是为了更细粒度的对相关逻辑进行布局约束。从设计层次角度讲,嵌套的Pblock对应的逻辑单元是父层与子层的关系。

看下面一个例子。模块arnd1和模块transformLoop[0].ct关系如下图所示。对这两个模块分别画Pblock,得到pblock_arnd1和pblock_transformLoop[0].ct,这两个pblock是嵌套的。

对于嵌套的pblock,它们在Physical Constraints窗口中也是按层次方式显示的,如下图所示。这样就可以清晰且直观地看到pblock的关系。

嵌套的两个pblock,它们的一些属性是不相同的。最典型的是PARENT不同,如下图所示。顶层的pblock其PARENT值为ROOT,而子层的pblock其PARENT是顶层的pblock。

pblock是否可以包含多个矩形

Vivado还支持创建多个矩形构成一个pblock,从而使得该pblock形状不是矩形。这在某些场合是非常有用的。相应的操作非常简单。

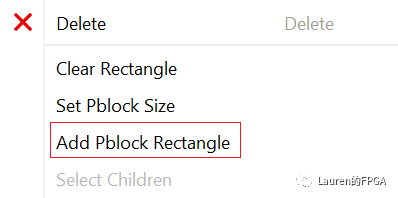

首先,对指定的cell创建一个pblock;其次,在Device View中选中该pblock,点击右键,选择Add Pblock Rectangle,如下图所示。此时会创建一个新的矩形。这两个矩形共同构成一个新的pblock。可以反复选中pblock,点击右键添加多个矩形pblock,从而形成多个矩形pblock共同构成一个非矩形的pblock。

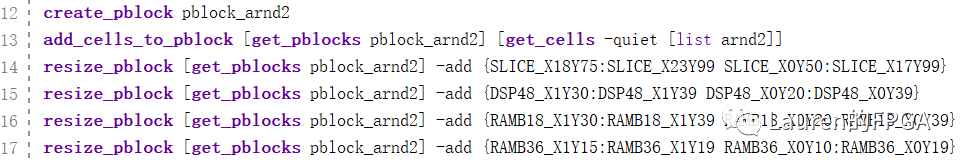

对于多个矩形构成一个pblock的情形,这些矩形之间会以虚线形式连接,表面它们隶属于同一个pblock。如下图所示。从Tcl命令角度讲,无非是增加了几行resize_pblock命令而已。

pblock是否可以占据整个Clock Region

此外,pblock的大小可以是整个时钟区域(Clock Region,包括相应的IO Bank)。只需要在画pblock时,将整个时钟区域框住即可,如下图所示。

此时,相应的Tcl命令就很简单,可以看到只需要一条resize_pblock命令即可确定pblock的大小和位置。实际上,在SSI芯片设计中,给每个die画一个大的pblock时(整个Pblock将整个die包含其中),只用指定左下角和右上角的时钟区域坐标即可。